دارة متكاملة ثلاثية الأبعاد

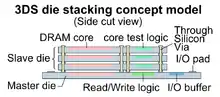

دارة متكاملة ثلاثية الأبعاد بالإنجليزية (three-dimensional integrated circuit) وإختصارا ب (3D IC) هو موسفت (أكسيد معدني من أشباه الموصلات) ل الدوائر المتكاملة المصنعة بطريقة التراص باستخدام رقائق السليكون وربط عموديا باستخدام، من خلال فيا (TSVs) والسليكون والنحاس على سبيل المثال، من خلال فيا بحيث تتصرف كجهاز واحد لتحقيق تحسينات في الأداء بطاقة منخفضة وبصمة أصغر من العمليات التقليدية ثنائية الأبعاد. التقنية ثلاثية الأبعاد هي أحد مخططات التكامل ثلاثية الأبعاد العديدة التي تستغل الاتجاه z لتحقيق فوائد الأداء الكهربائي في الإلكترونيات الدقيقة والإلكترونيات النانوية.

يمكن تصنيف الدوائر المتكاملة ثلاثية الأبعاد من خلال مستوى التسلسل الهرمي للتوصيل البيني على المستوى العالمي (الحزمة) والوسيط (لوحة السندات) والمحلي (الترانزستور).[1] بشكل عام، يعد التكامل ثلاثي الأبعاد مصطلحًا واسعًا يتضمن تقنيات مثل التعبئة والتغليف على مستوى الرقاقة ثلاثية الأبعاد (3DWLP)؛ 2.5D و 3D التكامل القائم على التداخل؛ ثلاثية الأبعاد مكدسة المرحلية (3D-SICs)؛ متجانسة 3D المرحلية. تكامل غير متجانس ثلاثي الأبعاد؛ وتكامل الأنظمة ثلاثية الأبعاد.[2]

عملت المنظمات الدولية مثل (JIC) وخريطة طريق التكنولوجيا الدولية لأشباه الموصلات (ITRS) على تصنيف مختلف تقنيات التكامل ثلاثية الأبعاد لتعزيز وضع المعايير وخرائط الطريق للتكامل ثلاثي الأبعاد.[3] اعتبارًا من 2010، 3D تستخدم الدوائر المتكاملة على نطاق واسع لذاكرة فلاش وميضية وفي الأجهزة المحمولة.

الأنواع

دارة ثلاثية الأبعاد مقابل التغليف ثلاثي الأبعاد

يشير التغليف ثلاثي الأبعاد إلى مخططات التكامل ثلاثية الأبعاد التي تعتمد على الطرق التقليدية للتوصيل البيني مثل ربط الأسلاك ورقاقة الوجه لتحقيق التكديس الرأسي. يمكن نشر العبوات ثلاثية الأبعاد بشكل أكبر في نظام ثلاثي الأبعاد في حزمة (اس أي بي ثلاثي الابعاد) وحزمة مستوى الرقاقة ثلاثية الأبعاد (3D WLP)، قالب ذاكرة مكدس مترابط مع روابط سلكية، وتكوينات الحزمة على العبوة (بي أو بي) المترابطة إما بالسندات السلكية، أو رقائق الوجه هي (اس أي بي اس ثلاثي الابعاد) التي كانت في التصنيع السائد لبعض الوقت ولديها بنية تحتية راسخة. يتم استخدام بي أو بي للتكامل الرأسي للتقنيات المتباينة مثل 3D WLP الذي يستخدم عمليات مستوى الرقاقة مثل طبقات إعادة التوزيع (RDL) وعمليات ارتطام الرقاقات لتشكيل روابط بينية.

يمكن تقسيم الدوائر المتكاملة إلى دوائر متكاملة ثلاثية الأبعاد مكدسة (3D SIC)، والتي تشير إلى تكديس شرائح IC باستخدام وصلات TSV ، وثلاثية الأبعاد متجانسة الدوائر المتكاملة، التي تستخدم عمليات fab لتحقيق الترابطات ثلاثية الأبعاد على المستويات المحلية من التسلسل الهرمي للأسلاك على الرقاقة على النحو المنصوص عليه في ITRS ، ينتج عن ذلك روابط رأسية مباشرة بين طبقات الجهاز. تظهر الأمثلة الأولى للنهج الأحادي في أجهزة V-NAND ثلاثية الأبعاد من سامسونج. [4]

اعتبارًا من 2010، 3D تُستخدم حزم IC على نطاق واسع لذاكرة فلاش NAND في الأجهزة المحمولة.[5]

يتطلب سوق الإلكترونيات الرقمية شريحة ذاكرة أشباه الموصلات عالية الكثافة لتلبية مكونات وحدة المعالجة المركزية التي تم إصدارها مؤخرًا، وقد تم اقتراح تقنية تكديس القوالب المتعددة كحل لهذه المشكلة. كشفت جمعية تكنولوجيا الحالة الصلبة أن تقنية ذاكرة وصول عشوائي ديناميكية القادمة تتضمن خطة تكديس القوالب "3D SiC" في «منتدى ذاكرة الخادم»، 1 - 2 نوفمبر 2011، سانتا كلارا، كاليفورنيا. في أغسطس 2014، بدأت إلكترونيات سامسونج في إنتاج 64 وحدات GB إس دي رام للخوادم القائمة على ذاكرة دي دي آر 4 (معدل بيانات مزدوج 4) باستخدام تقنية حزمة 3D TSV.[6] تشتمل المعايير الجديدة المقترحة للذاكرة الحيوية المكدسة ثلاثية الأبعاد على إدخال / إخراج عريض، وإدخال / إخراج عريض 2، ومكعب ذاكرة هجين، وذاكرة عرض النطاق الترددي العالي

التصميم الثلاثي الابعاد المتجانسة

هناك عدة طرق لتصميم IC ثلاثي الأبعاد، بما في ذلك طرق إعادة التبلور وربط الرقائق. هناك نوعان رئيسيان من روابط الرقاقة، وصلات النحاس إلى النحاس (وصلات من النحاس إلى النحاس بين الدوائر المتكاملة المكدسة، والمستخدمة في TSVs) [7] [8] وعبر السيليكون عبر (TSV). اعتبارًا من عام 2014، تم إطلاق عدد من منتجات الذاكرة مثل ذاكرة النطاق الترددي العالي (HBM) ومكعب ذاكرة هجين التي تنفذ 3D التراص IC مع TSVs. هناك عدد من مناهج تكديس المفاتيح التي يتم تنفيذها واستكشافها. وتشمل هذه:

دي تو - دي

المكونات الإلكترونية مبنية على قوالب متعددة، والتي يتم محاذاتها وربطها فيما بعد. يمكن إجراء ترقق وخلق TSV قبل أو بعد الترابط. تتمثل إحدى ميزات دي تو دي في أنه يمكن اختبار كل قالب مكون أولاً، بحيث لا يفسد قالب واحد سيئ مجموعة كاملة. علاوة على ذلك، يموت كل منهم في 3D يمكن وضع IC في سلة المهملات مسبقًا، بحيث يمكن مزجها ومطابقتها لتحسين استهلاك الطاقة والأداء (على سبيل المثال، مطابقة العديد من النرد من زاوية معالجة الطاقة المنخفضة لتطبيق الهاتف المحمول).

المكونات الإلكترونية مبنية على اثنين من رقائق أشباه الموصلات. رقاقة واحدة مقطعة إلى مكعبات. يتم محاذاة النرد المفرد وإلصاقه بمواقع الرقاقة الثانية. كما هو الحال في طريقة الرقاقة على الرقاقة، يتم إجراء التخفيف وإنشاء TSV إما قبل أو بعد الترابط. يمكن إضافة قالب إضافي إلى الأكوام قبل التكعيب.[9]

دي تو - ويفر

المكونات الإلكترونية مبنية على اثنين من رقائق أشباه الموصلات. رقاقة واحدة مقطعة إلى مكعبات. يتم محاذاة النرد المفرد وإلصاقه بمواقع الرقاقة الثانية. كما هو الحال في طريقة الرقاقة على الرقاقة، يتم إجراء التخفيف وإنشاء TSV إما قبل أو بعد الترابط. يمكن إضافة قالب إضافي إلى الأكوام قبل التكعيب. [9]

ويفر تو ويفر

المكونات الإلكترونية مبنية على اثنين أو أكثر من رقائق أشباه الموصلات، والتي يتم محاذاتها، وربطها، وتقطيعها إلى مكعبات ثلاثية الأبعاد المرحلية. يمكن تخفيف كل رقاقة قبل أو بعد الترابط. إما أن تكون الوصلات العمودية مدمجة في الرقائق قبل الترابط أو يتم إنشاؤها في المكدس بعد الترابط. تمر هذه «عبر فتحات السيليكون» (TSVs) عبر ركيزة (ركائز) السيليكون بين الطبقات النشطة و / أو بين طبقة نشطة ولوحة رابطة خارجية. يمكن أن يؤدي ربط الرقاقة إلى الرقاقة إلى تقليل العوائد، لأنه إذا كان هناك أي 1 من رقائق N في صورة ثلاثية الأبعاد IC معيبة، 3D بأكمله سيكون IC معيبًا. علاوة على ذلك، يجب أن تكون الرقاقات بنفس الحجم، لكن العديد من المواد الغريبة (على سبيل المثال، III-Vs) على رقاقات أصغر بكثير من منطق سيموس أو ذاكرة وصول عشوائي ديناميكية (عادة 300 مم)، مما يعقد التكامل غير المتجانس.

الفوائد

بينما تعمل عمليات تحجيم CMOS التقليدية على تحسين سرعة انتشار الإشارة، فإن التحجيم من تقنيات التصنيع وتصميم الرقائق الحالية أصبح أكثر صعوبة وتكلفة، ويرجع ذلك جزئيًا إلى قيود كثافة الطاقة، وجزئيًا لأن التوصيلات البينية لا تصبح أسرع بينما تعمل الترانزستورات. 3D تتعامل الدوائر المتكاملة مع تحدي القياس عن طريق تكديس قوالب ثنائية الأبعاد وربطها في البعد الثالث. يعد هذا بتسريع الاتصال بين الرقائق ذات الطبقات، مقارنة بالتخطيط المستوي. 3D تعد ICs بالعديد من الفوائد المهمة، بما في ذلك:

اثار

المزيد من الوظائف تتناسب مع مساحة صغيرة. هذا يوسع قانون مور ويتيح جيلًا جديدًا من الأجهزة الصغيرة ولكنها قوية.

كلفة

- يمكن أن يؤدي تقسيم شريحة كبيرة إلى قوالب متعددة أصغر باستخدام التراص ثلاثي الأبعاد إلى تحسين الإنتاجية وتقليل تكلفة التصنيع إذا تم اختبار القوالب الفردية بشكل منفصل.

تكامل غير متجانس

يمكن بناء طبقات الدوائر بعمليات مختلفة، أو حتى على أنواع مختلفة من الرقاقات. هذا يعني أنه يمكن تحسين المكونات بدرجة أكبر بكثير مما لو تم بناؤها معًا على رقاقة واحدة. علاوة على ذلك، يمكن دمج المكونات ذات التصنيع غير المتوافق في صورة ثلاثية الأبعاد واحدة IC.

ربط أقصر

يتم تقليل متوسط طول السلك. الأرقام الشائعة التي أبلغ عنها الباحثون هي في حدود 10-15٪، ولكن هذا التخفيض ينطبق في الغالب على الاتصال البيني الأطول، والذي قد يؤثر على تأخير الدائرة بمقدار أكبر. بالنظر إلى أن الأسلاك ثلاثية الأبعاد لها سعة أعلى بكثير من الأسلاك التقليدية داخل القالب، فقد يتحسن تأخير الدائرة وقد لا يتحسن.

قوة

يمكن أن يؤدي الاحتفاظ بإشارة على الرقاقة إلى تقليل استهلاكها للطاقة بمقدار 10-100 مرة. تقلل الأسلاك القصيرة أيضًا من استهلاك الطاقة من خلال إنتاج سعة أقل من الطفيلية. يؤدي تقليل ميزانية الطاقة إلى تقليل توليد الحرارة وإطالة عمر البطارية وانخفاض تكلفة التشغيل.

تصميم

يضيف البعد الرأسي ترتيبًا أعلى للاتصال ويوفر إمكانيات تصميم جديدة.

أمن الدائرة

يمكن للتكامل ثلاثي الأبعاد تحقيق الأمن من خلال الغموض؛ يعقد الهيكل المكدس محاولات عكس هندسة الدوائر. يمكن أيضًا تقسيم الدوائر الحساسة بين الطبقات بطريقة تحجب وظيفة كل طبقة. علاوة على ذلك، يسمح التكامل ثلاثي الأبعاد بدمج ميزات مخصصة تشبه شاشة النظام في طبقات منفصلة. الهدف هنا هو تنفيذ نوع من جدار حماية الأجهزة لأي مكونات / شرائح سلعة يتم مراقبتها في وقت التشغيل، في محاولة لحماية النظام الإلكتروني بأكمله من هجمات وقت التشغيل بالإضافة إلى تعديلات الأجهزة الضارة.

عرض النطاق

يسمح التكامل ثلاثي الأبعاد بأعداد كبيرة من الفتحات الرأسية بين الطبقات. يسمح ذلك ببناء حافلات ذات نطاق ترددي عريض بين الكتل الوظيفية في طبقات مختلفة. مثال نموذجي سيكون معالج + ذاكرة مكدس ثلاثي الأبعاد، مع ذاكرة التخزين المؤقت مكدسة أعلى المعالج. يسمح هذا الترتيب بحافلة أوسع بكثير من 128 أو 256 بت بين ذاكرة التخزين المؤقت والمعالج. تعمل الحافلات العريضة بدورها على تخفيف مشكلة جدار الذاكرة.

التحديات

لأن هذه التكنولوجيا جديدة فهي تحمل تحديات جديدة منها:

- كلفة

- في حين أن التكلفة هي فائدة عند مقارنتها مع القياس، فقد تم تحديدها أيضًا على أنها تحدٍ لتسويق 3D المرحلية في تطبيقات المستهلك السائدة. ومع ذلك، يجري العمل على معالجة هذا. على الرغم من أن التكنولوجيا ثلاثية الأبعاد جديدة ومعقدة إلى حد ما، فإن تكلفة عملية التصنيع واضحة بشكل مدهش عند تقسيمها إلى الأنشطة التي تبني العملية بأكملها. من خلال تحليل مجموعة الأنشطة التي تكمن في القاعدة، يمكن تحديد محركات التكلفة. بمجرد تحديد محركات التكلفة، يصبح مسعى أقل تعقيدًا لتحديد مصدر غالبية التكلفة، والأهم من ذلك، أين يمكن تخفيض التكلفة.[10]

- أثمر

- تضيف كل خطوة تصنيع إضافية خطر حدوث عيوب. من أجل 3D تكون الدوائر المتكاملة قابلة للتطبيق تجاريًا، ويمكن إصلاح العيوب أو تحملها، أو يمكن تحسين كثافة الخلل.

- يسخن

- يجب تبديد الحرارة المتراكمة داخل الكومة. هذه مشكلة حتمية لأن القرب الكهربائي يرتبط بالتقارب الحراري. يجب إدارة النقاط الساخنة الحرارية المحددة بعناية أكبر.

- تعقيد التصميم

- تتطلب الاستفادة الكاملة من التكامل ثلاثي الأبعاد تقنيات تصميم متطورة وأدوات CAD جديدة.

- عرض TSV النفقات العامة

- TSVs كبيرة مقارنة بالبوابات ومخططات الأرضيات. في 45 عقدة تقنية نانومتر، فإن مساحة مساحة 10 ميكرومتر × 10 ميكرومتر TSV يمكن مقارنتها بحوالي 50 بوابة. علاوة على ذلك، تتطلب قابلية التصنيع منصات هبوط ومناطق مانعة تزيد من بصمة منطقة TSV. اعتمادًا على اختيارات التكنولوجيا، تقوم TSVs بحظر بعض المجموعات الفرعية من موارد التخطيط. يتم تصنيع TSVs عبر أول قبل المعدنة، وبالتالي تحتل طبقة الجهاز وتؤدي إلى عوائق التنسيب. يتم تصنيع TSVs عبر-last بعد المعدنة وتمر عبر الشريحة. وبالتالي، فإنها تشغل كلاً من الجهاز والطبقات المعدنية، مما يؤدي إلى وضع العوائق وتوجيهها. بينما يُتوقع عمومًا أن يؤدي استخدام TSVs إلى تقليل طول الأسلاك، فإن هذا يعتمد على عدد TSVs وخصائصها. أيضًا، تؤثر دقة التقسيم الداخلي على طول الأسلاك. يتناقص عادةً بالنسبة للحبيبات المتوسطة (الكتل ذات 20-100 وحدة نمطية) والخشنة (التقسيم على مستوى الكتلة)، ولكنه يزداد بالنسبة للحبيبات الدقيقة (التقسيم على مستوى البوابة).

- اختبارات

- لتحقيق عائد إجمالي مرتفع وتقليل التكاليف، يعد الاختبار المنفصل للقوالب المستقلة أمرًا ضروريًا. ومع ذلك، تكامل محكم بين الطبقات النشطة المجاورة في 3D تستلزم الدوائر المتكاملة قدرًا كبيرًا من الترابط بين الأقسام المختلفة من نفس وحدة الدائرة التي تم تقسيمها إلى قوالب مختلفة. بصرف النظر عن الحمل الهائل الذي قدمته TSVs المطلوبة، لا يمكن اختبار أقسام مثل هذه الوحدة، على سبيل المثال، المضاعف، بشكل مستقل عن طريق التقنيات التقليدية. ينطبق هذا بشكل خاص على مسارات التوقيت الحرجة الموضوعة في 3D.

- نقص المعايير

- هناك القليل من المعايير للأبعاد الثلاثية المستندة إلى TSV تصميم وتصنيع وتعبئة IC ، على الرغم من معالجة هذه المشكلة. بالإضافة إلى ذلك، هناك العديد من خيارات التكامل التي يتم استكشافها مثل عبر الأخير، عبر الأول، عبر الوسط؛ المتدخلون أو الترابط المباشر؛ إلخ.

- سلسلة التوريد التكامل غير المتجانسة

- في الأنظمة المتكاملة بشكل غير متجانس، يؤدي تأخير جزء واحد من أحد موردي الأجزاء المختلفين إلى تأخير تسليم المنتج بالكامل، وبالتالي يؤخر الإيرادات لكل من الأجزاء ثلاثية الأبعاد موردي أجزاء IC.

- عدم وجود ملكية محددة بوضوح

- ليس من الواضح من الذي يجب أن يمتلك 3D التكامل والتعبئة / التجميع IC. يمكن أن تكون بيوت التجميع مثل هندسة أشباه الموصلات المتقدمة أو مصنعي المعدات الأصلية للمنتج.

أنماط التصميم

اعتمادًا على تقسيم التقسيم، يمكن تمييز أنماط تصميم مختلفة. يواجه التكامل على مستوى البوابة تحديات متعددة ويبدو حاليًا أقل عملية من التكامل على مستوى الكتلة.

- التكامل على مستوى البوابة

- هذا النمط يقسم الخلايا القياسية بين العديد من القوالب. يعد بتقليل طول الأسلاك ومرونة كبيرة. ومع ذلك، قد يتم تقويض تقليل طول الأسلاك ما لم يتم الحفاظ على وحدات ذات حجم أدنى معين. من ناحية أخرى، تشمل آثاره الضارة العدد الهائل من TSVs اللازمة للوصلات البينية. يتطلب نمط التصميم هذا أدوات تحديد المكان والطريق ثلاثية الأبعاد، وهي غير متوفرة حتى الآن. أيضًا، يعني تقسيم كتلة التصميم عبر قوالب متعددة أنه لا يمكن اختبارها بالكامل قبل تكديس القوالب. بعد تكديس القوالب (اختبار ما بعد السندات)، يمكن أن يؤدي فشل قالب واحد إلى جعل العديد من القوالب الجيدة غير صالحة للاستعمال، مما يقوض العائد. يعمل هذا النمط أيضًا على تضخيم تأثير تباين العملية، وخاصة الاختلاف بين القوالب. في الواقع، قد ينتج عن التخطيط ثلاثي الأبعاد نتائج سيئة أكثر من نفس الدائرة الموضحة في 2D ، على عكس الوعد الأصلي لـ 3D تكامل IC. علاوة على ذلك، يتطلب أسلوب التصميم هذا إعادة تصميم الملكية الفكرية المتاحة، نظرًا لأن كتل IP الحالية وأدوات EDA لا توفر تكامل ثلاثي الأبعاد.

- التكامل على مستوى الكتلة

- يعين هذا النمط كتل تصميم كاملة لفصل القوالب. تستوعب كتل التصميم معظم توصيلات netlist وترتبط بعدد صغير من الوصلات البينية العالمية. لذلك، يعد التكامل على مستوى الكتلة بتقليل عبء TSV. تتطلب الأنظمة ثلاثية الأبعاد المتطورة التي تجمع بين القوالب غير المتجانسة عمليات تصنيع متميزة في عقد تقنية مختلفة لمنطق عشوائي سريع ومنخفض الطاقة، وأنواع ذاكرة متعددة، ودوائر تمثيلية وترددات لاسلكية، وما إلى ذلك. وبالتالي، فإن التكامل على مستوى الكتلة، والذي يسمح بعمليات تصنيع منفصلة ومحسّنة، يبدو حاسمًا للتكامل ثلاثي الأبعاد. علاوة على ذلك، قد يسهل هذا النمط الانتقال من التصميم ثنائي الأبعاد الحالي إلى التصميم ثلاثي الأبعاد تصميم IC. في الأساس، أدوات الإدراك ثلاثي الأبعاد مطلوبة فقط للتقسيم والتحليل الحراري. سيتم تصميم قوالب منفصلة باستخدام أدوات (معدلة) ثنائية الأبعاد وكتل ثنائية الأبعاد. والدافع وراء ذلك هو التوافر الواسع لكتل IP الموثوقة. من الأنسب استخدام كتل IP ثنائية الأبعاد المتاحة ووضع TSVs الإلزامية في المساحة الخالية بين الكتل بدلاً من إعادة تصميم كتل IP وتضمين TSVs. تعد هياكل التصميم من أجل الاختبار مكونًا رئيسيًا لكتل IP ، وبالتالي يمكن استخدامها لتسهيل اختبار الأبعاد الثلاثية المرحلية. أيضًا، يمكن تضمين المسارات الحرجة في الغالب داخل كتل ثنائية الأبعاد، مما يحد من تأثير TSV والتباين بين القوالب على إنتاجية التصنيع. أخيرًا، غالبًا ما يتطلب تصميم الرقاقة الحديث تغييرات هندسية في اللحظة الأخيرة. تقييد تأثير هذه التغييرات على وفاة واحدة أمر ضروري للحد من التكلفة.

- تم اختراع أول رقائق مكدسة ثلاثية الأبعاد ثلاثية الأبعاد مصنوعة من خلال السيليكون عبر عملية (TSV) في اليابان في الثمانينيات. سجلت شركة هيتاشي براءة اختراع يابانية في عام 1983، تلتها شركة فوجيتسو في عام 1984. في عام 1986، وصفت براءة اختراع يابانية مقدمة من شركة فوجيتسو بنية رقاقات مكدسة باستخدام TSV.[11] في عام 1989، كان ميتسوماسا كويوناجي من جامعة توهوكو رائدًا في تقنية ربط الرقاقة مع TSV ، والتي استخدمها لتصنيع شريحة LSI ثلاثية الأبعاد في عام 1989. [11] [12] [13] في عام 1999، بدأت رابطة تقنيات الإلكترونيات المتقدمة الفائقة (ASET) في اليابان في تمويل تطوير تقنية 3D شرائح IC التي تستخدم تقنية TSV ، تسمى مشروع «البحث والتطوير في تقنية تكامل الأنظمة الإلكترونية عالية الكثافة». [11] [14] صاغ مصطلح «عبر السيليكون عبر» (TSV) باحثو Tru-Si Technologies سيرجي سافاستيوك، وسنياغويني، وكورتزينسكي، الذين اقترحوا طريقة TSV لحل تغليف على مستوى رقاقة ثلاثي الأبعاد (WLP) في عام 2000.[15]

- استخدمت مجموعة كوياناجي في جامعة توهوكو، بقيادة ميتسوماسا كوياناجي، تقنية TSV لتصنيع شريحة ذاكرة ثلاثية الطبقات في عام 2000، وشريحة شبكية اصطناعية من ثلاث طبقات في عام 2001، ومعالج دقيق ثلاثي الطبقات في عام 2002، وذاكرة من عشر طبقات رقاقة في عام 2005. [12] في العام نفسه، قدم فريق بحثي بجامعة ستانفورد يتألف من كاوستاف بانيرجي وشكري ج.صوري وباوان كابور وكريشنا سي ساراسوات تصميمًا جديدًا لشريحة ثلاثية الأبعاد يستغل البعد الرأسي للتخفيف من مشاكل الترابط ذات الصلة ويسهل التكامل غير المتجانس للتقنيات مع تحقيق تصميم نظام على شريحة (SoC).[16] [17]

أوروبا (1988 – 2005)

بدأ فراونهوفر وسيمنز البحث عن الأبعاد الثلاثية تكامل IC في عام 1987. [11] في عام 1988، قاموا بتصنيع أجهزة 3D CMOS IC على أساس إعادة بلورة بولي سيليكون.[18] في عام 1997، تم تطوير طريقة انتر شيب عبر (ICV) بواسطة – سيمنس بما في ذلك بيتر رام ومانفرد انجيهرت وفيرنر باملر وكريستوف لاندسبيرج وارمين كلومب.[19] كان أول 3D الصناعية عملية IC ، بناءً على رقائق سيمنز سيمس الرائعة. تم لاحقًا تسمية أحد أشكال عملية TSV تلك بتقنية TSV-SLID (الانتشار البيني السائل الصلب).[20] لقد كان نهجًا لـ 3D يعتمد تصميم IC على الترابط ذو درجة الحرارة المنخفضة والتكامل الرأسي لأجهزة IC باستخدام فتحات بين الشرائح، والتي حصلت على براءة اختراع لها.

في أوائل العقد الأول من القرن الحادي والعشرين، قام فريق من باحثي فراونهوفر وإنفينيون ميونيخ بالتحقيق في تقنيات 3D TSV مع التركيز بشكل خاص على التكديس من القالب إلى الركيزة ضمن مشروع ايوريكا الألماني / النمساوي VSI وبدأ مشروع التكامل الأوروبي أي سيوبس، كأول ثلاثي الأبعاد أوروبي منصة التكنولوجيا، واي بريانس مع وإنفينيون ، وسيمونس ، وايفيل ، واي ام أي سي ، وتيندال ، حيث تم تصنيع وتقييم أنظمة متكاملة ثلاثية الأبعاد غير متجانسة. كان التركيز بشكل خاص على مشروع أي برانس هو تطوير عمليات درجة حرارة منخفضة جديدة لأنظمة استشعار متكاملة ثلاثية الأبعاد عالية الموثوقية.[21]

الولايات المتحدة الأمريكية (1999 – 2012)

في عام 2004، قامت شركة تيزيرن سيميكونديتيون [22] ببناء أجهزة ثلاثية الأبعاد عاملة من ستة تصميمات مختلفة. تم بناء الرقائق في طبقتين مع TSVs من التنجستن «عبر الأول» للتوصيل البيني الرأسي. تم تكديس اثنين من رقائق الويفر وجهاً لوجه وربطها بعملية النحاس. تم تخفيف الرقاقة العلوية ثم تم تقطيع مكدس الويفر المكون من اثنين إلى مكعبات. كانت الشريحة الأولى التي تم اختبارها عبارة عن سجل ذاكرة بسيط ، ولكن أبرزها كان معالج / مكدس ذاكرة 8051 [23] الذي أظهر سرعة أعلى بكثير واستهلاك أقل للطاقة من تجميع ثنائي الأبعاد مشابه.

في عام 2004، قدمت إنتل نسخة ثلاثية الأبعاد من وحدة المعالجة المركزية بنتييوم4. تم تصنيع الرقاقة بقولبتين باستخدام التكديس وجهاً لوجه ، مما سمح بتكثيف الهيكل. يتم استخدام TSVs المؤخرة للإدخال / الإخراج وإمدادات الطاقة. بالنسبة إلى مخطط الأرضية ثلاثي الأبعاد ، قام المصممون يدويًا بترتيب الكتل الوظيفية في كل قالب بهدف تقليل الطاقة وتحسين الأداء. سمح تقسيم الكتل الكبيرة والعالية الطاقة وإعادة الترتيب بعناية للحد من النقاط الساخنة الحرارية. يوفر التصميم ثلاثي الأبعاد تحسينًا في الأداء بنسبة 15٪ (بسبب التخلص من مراحل خطوط الأنابيب) وتوفير الطاقة بنسبة 15٪ (بسبب إزالة أجهزة إعادة الإرسال وتقليل الأسلاك) مقارنةً بـ 2D بنتييوم 4.

شريحة تيرافلوبس التي قدمتها إنتل في عام 2007 هي تصميم تجريبي مكون من 80 نواة مع ذاكرة مكدسة. نظرًا لارتفاع الطلب على عرض النطاق الترددي للذاكرة ، فإن نهج الإدخال / الإخراج التقليدي سيستهلك من 10 إلى 25 W. لتحسين ذلك ، طبق مصممو إنتل ناقل ذاكرة يعتمد على TSV. يتم توصيل كل نواة ببلاطة ذاكرة واحدة في قالب SRAM مع ارتباط يوفر 12 عرض النطاق الترددي GB / s ، مما يؤدي إلى عرض نطاق ترددي إجمالي قدره 1 تيرابايت / ثانية أثناء استهلاك 2.2 فقط دبليو.

مرحلة ثلاثي الابعاد التجاري (2004 – حتى الآن)

تستخدم ذاكرة النطاق الترددي العالي ، التي طورتها سامسونج واي ام دي، رقائق مكدسة تم تصنيع أول شريحة ذاكرة HBM بواسطة إس كيه هاينكس في عام 2013.[24] في يناير 2016، أعلنت شركة إلكترونيات سامسونج عن الإنتاج الضخم المبكر لـ HBM2 ، حتى 8 غيغابايت لكل مكدس.[25] [26]

انظر أيضًا

المراجع

- "SEMI.ORG" (PDF)، مؤرشف من الأصل (PDF) في 24 سبتمبر 2015.

- "What is 3D Integration? - 3D InCites"، مؤرشف من الأصل في 30 ديسمبر 2014.

- "INTERNATIONAL TECHNOLOGY ROADMAP FOR SEMICONDUCTORS 2011 EDITION" (PDF)، مؤرشف من الأصل (PDF) في 30 ديسمبر 2014، اطلع عليه بتاريخ 30 ديسمبر 2014.

- "Comparing Samsung's 3D NAND with Traditional 3D ICs"، 16 أغسطس 2013، مؤرشف من الأصل في 3 مارس 2021.

- James, Dick (2014)، "3D ICs in the real world"، 25th Annual SEMI Advanced Semiconductor Manufacturing Conference (ASMC 2014): 113–119، doi:10.1109/ASMC.2014.6846988، ISBN 978-1-4799-3944-2، مؤرشف من الأصل في 26 أبريل 2021.

- "Samsung starts production of 3D DDR4 DRAM modules"، 27 أغسطس 2014، مؤرشف من الأصل في 31 ديسمبر 2014.

- Maestre Caro, A.؛ Travaly, Y.؛ Maes, G.؛ Borghs, G.؛ Armini, S. (2011)، "Enabling Cu-Cu connection in (Dual) damascene interconnects by selective deposition of two different SAM molecules"، 2011 IEEE International Interconnect Technology Conference، ص. 1–3، doi:10.1109/IITC.2011.5940263، ISBN 978-1-4577-0503-8.

- Reif, Rafael؛ Tan, Chuan Seng؛ Fan, Andy؛ Chen, Kuan-Neng؛ Das, Shamik؛ Checka, Nisha (2002)، "3-D Interconnects Using Cu Wafer Bonding: Technology and Applications" (PDF)، Advanced Metallization Conference: 37–44، مؤرشف من الأصل (PDF) في 15 يوليو 2019، اطلع عليه بتاريخ 15 يوليو 2019.

- Chen, D.Y.؛ Chiou, W.C.؛ Chen, M.F.؛ Wang, T.D.؛ Ching, K.M.؛ Tu, H.J.؛ Wu, W.J.؛ Yu, C.L.؛ Yang, K.F. (2009)، "Enabling 3D-IC foundry technologies for 28 nm node and beyond: through-silicon-via integration with high throughput die-to-wafer stacking"، 2009 IEEE International Electron Devices Meeting (IEDM)، ص. 1–4، doi:10.1109/IEDM.2009.5424350، ISBN 978-1-4244-5639-0.

- A. Palesko, The Cost of 3D ICs, 3D InCites Knowledge Portal, January 9, 2015 "The Cost of 3D ICs"، 09 يناير 2015، مؤرشف من الأصل في 09 يناير 2015، اطلع عليه بتاريخ 09 يناير 2015.

- Kada, Morihiro (2015)، "Research and Development History of Three-Dimensional Integration Technology" (PDF)، Three-Dimensional Integration of Semiconductors: Processing, Materials, and Applications، Springer، ص. 8–13، ISBN 9783319186757.

- Fukushima, T.؛ Tanaka, T.؛ Koyanagi, Mitsumasa (2007)، "Thermal Issues of 3D ICs" (PDF)، SEMATECH، جامعة توهوكو، مؤرشف من الأصل (PDF) في 16 مايو 2017، اطلع عليه بتاريخ 16 مايو 2017.

- Tanaka, Tetsu؛ Lee, Kang Wook؛ Fukushima, Takafumi؛ Koyanagi, Mitsumasa (2011)، "3D Integration Technology and Heterogeneous Integration"، سيمانتك سكولر، مؤرشف من الأصل في 8 مارس 2021، اطلع عليه بتاريخ 19 يوليو 2019.

- Takahashi, Kenji؛ Tanida, Kazumasa (2011)، "Vertical Interconnection by ASET"، Handbook of 3D Integration, Volume 1: Technology and Applications of 3D Integrated Circuits، John Wiley & Sons، ص. 339، ISBN 9783527623068.

- Savastionk, S.؛ Siniaguine, O.؛ Korczynski, E. (2000)، "Thru-silicon vias for 3D WLP"، Proceedings International Symposium on Advanced Packaging Materials Processes, Properties and Interfaces (Cat. No.00TH8507): 206–207، doi:10.1109/ISAPM.2000.869271، ISBN 0-930815-59-9.

- Lavanyashree, B.J. (أغسطس 2016)، "3-Dimensional (3D) ICs: A Survey" (PDF)، International Journal of Digital Application & Contemporary Research، 5 (1)، مؤرشف من الأصل (PDF) في 04 مارس 2019.

- Banerjee, Kaustav؛ Souri, Shukri J.؛ Kapur, Pawan؛ Saraswat, Krishna C. (2001)، "3-D ICs: a novel chip design for improving deep-submicrometer interconnect performance and systems-on-chip integration"، Proceedings of the IEEE، 89 (5): 602–633، doi:10.1109/5.929647، ISSN 0018-9219.

- Ramm, Peter (22 يناير 2016)، "Fraunhofer EMFT: Our Early and Ongoing Work in 3D Integration"، 3D InCites، مؤرشف من الأصل في 8 مارس 2021، اطلع عليه بتاريخ 22 سبتمبر 2019.

- Ramm, P.؛ Bollmann, D.؛ Braun, R.؛ Buchner, R.؛ Cao-Minh, U.؛ وآخرون (نوفمبر 1997)، "Three dimensional metallization for vertically integrated circuits"، Microelectronic Engineering، 37–38: 39–47، doi:10.1016/S0167-9317(97)00092-0.

- Macchiolo, A.؛ Andricek, L.؛ Moser, H. G.؛ Nisius, R.؛ Richter, R. H.؛ Weigell, P. (01 يناير 2012)، "SLID-ICV Vertical Integration Technology for the ATLAS Pixel Upgrades"، Physics Procedia، 37: 1009–1015، arXiv:1202.6497، Bibcode:2012PhPro..37.1009M، doi:10.1016/j.phpro.2012.02.444، ISSN 1875-3892.

- "HOME"، مؤرشف من الأصل في 11 أبريل 2021.

- "Tezzaron Semiconductor: The Z Path Forward"، Tezzaron Semiconductor، مؤرشف من الأصل في 10 مايو 2021، اطلع عليه بتاريخ 19 يوليو 2019.

- Cole, Bernard، "Terrazon applies 3D stacking technology to 8051 MCU core"، EETimes، مؤرشف من الأصل في 17 سبتمبر 2020، اطلع عليه بتاريخ 10 أغسطس 2020.

- "History: 2010s"، SK Hynix، مؤرشف من الأصل في 17 مايو 2021، اطلع عليه بتاريخ 08 يوليو 2019.

- "Samsung Begins Mass Producing World's Fastest DRAM – Based on Newest High Bandwidth Memory (HBM) Interface"، news.samsung.com، مؤرشف من الأصل في 11 نوفمبر 2021.

- "Samsung announces mass production of next-generation HBM2 memory – ExtremeTech"، 19 يناير 2016، مؤرشف من الأصل في 17 مايو 2021.

- بوابة كهرباء

- بوابة الفيزياء

- بوابة تقانة