منطق مقاومة - ترانزستور

منطق مقاومة ترانزستور (الإنجليزية (Resistor–transistor logic (RTL) هو أحد عوائل الدوائر الرقمية المبنية من مقاحل ثنائية الوصلة (م ث أ - BJT)، وهو أيضا استخدم في بناء البوابات المنطقية (AND، على سبيل المثال) وجاء بعده بوابات أخرى مثل منطق ثنائي-ترانزستور(diode–transistor logic DTL) منطق ترانزستور ترانزستور (Transistor Transistor -TTL logic) دائرة المنطق كانت تبنى قبل اخراع الترازيستر باستخدام المكونات الاكترونية مثل المقاومة والمكثف. ولكن في عام 1961 خرج إلى النور أول عائلة منطقية بستخدام الترازيستور ومن ثم بدأت عملية تصنيع الدوائر المتكاملة التي استخدم في تصنيع الحاسب ابولوا الذي بدء في تصنيعه في عام 1961 وانتهى في عام 1966

العملية

عاكس منطق الترانزسيتر

ترانزستور ثنائي القطب هو ابسط البوابة المنطقية حيث يمكن عمل منه دائرة النفي NOT وهو عبارة عن توصيل الترانزستور ذي الباعث المشترك ويوضع الجهد كهربائي على مدخل القاعدة. كما يعتبر مخرج مرتفع 1 عندما يكون فرق الجهد على القاعدة اقل من 0.7 ويكون مخرج منخفض 0 عندما يكون فرق الجهد الداخل يكفي لتحويل الترانسيستر إلى وضع المشبع. الهدف من الجامع لتحويل التيار إلى جهد كهرابائي ويتم اختيار المقاومة كبيرة كفاية حتى تدخل التراتنسيتر في وضع الإشباع وصغيرة كفاية لتحسين الانتشار Fan-out.

عمل البوابة المنطقية NOR باستخدام ترانزستور واحد (منطق مقاوم ترانزستور)

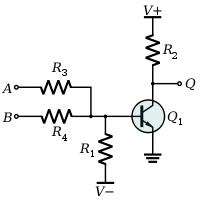

وضع مقاومتين أو أكثر على القاعدة (R3 وR4) بدلا من واحد، يصبح منطق مقاوم ترانزستور (RTL) ذو مدخللين بوابة اختيار سالبة NOR ذات مدخلين (انظر الشكل على اليسار). أو العملية المنطقية أو (OR) تتم عن طريق تطبيق على التوالي اثنين من العمليات الحسابية (الإضافة والمقارنة ).[1]

حالة (OR) مخرج منخفض 0 يساوي جهد الجامع في وضع التشبع ومخرج مرتفع 1 يساوي +V مطروح منه جهد الجامع في وضع التشبع، بينما هذه الدائرة قدرتها على قيادة دوائر أخرى تساوي صفر fan out=0

متعدد الترانزيستورات منطق مقاومة ترانزستور (RTL) وبوابة اختيار سالبة NOR

القيود المفروضة في حالة منطق مقاومة ترانزستور (RTL)بستخدام ترانزستور واحد يتم التغلب عليها من قبل الترانزستور الأخرى في RTL متعدد الترونسوسترات. وتتكون من مجموعة متوازية من الترانزستور التبديل يقودها RTL موجود على المداخل (انظر إلى الشكل على اليسار). وفي هذه التوزيعة، المدخلات مفصولة تماما وعدد المدخلات محدود ويدخل في وقع القطع CUT OFF مما يتسبب بخروج المخرج المرتفع 1 وبينما يكون أحد اطرافه في وضع الإشباع يكون المخرج منخفض 0 وهذه الفكرة استخدمة أيضا بعض البوابات الأخرى مثل DCTL, ECL, TTL (7450, 7460), NMOS وCMOS

مزايا

الميزة الرئيسية لتكنولوجيا منطق مقاوم ترانزستور RTL انها تستخدم عدد اقل من الترانزستورات بالمقارنة مع الدوائر المتكاملة. الترانزستورات كانت أغلى عنصر في الإنتاج. ومع انخفاض سعر الترانستور قامت شركات إنتاج الوابات المنطقية (مثل فيرتشايلد في 1961) بالنتقال إلى دوائر ذات مواصفات أفضل مثل منطق ثنائي-ترانزستور diode–transistor logic ثم إلى منطق ترانزستور ترانزستور – (ابتداء من عام 1963 في سيلفانيا).[3]

العيوب

عيب RTL هو استهلاكه الكبير للطاقة; عندما يكون الترانزستور في وضع التشغيل يستهلك الكثير الطاقة من خلال التيار المار في مقاومة الجامع والقاعدة. ولهذا تتولد حرارة في دوائر RTL . في المقابل، في دوائر TTL مع «الطوطم القطب» بالانجليزي Totem pole يقلل التيار وبدوره يقلل استهلاك الطاقة ويقلل أيضا الحرارة.

و عيب اخر في RTL انه قدرته على شبك دوائر منطقية أخرى في المدخل fan _in قليلة جدا وففي الوضع القياسي فانها تساوي 3 ولذلك فهي تسبب مشكلة للعديد من تصاميم الدوائر الكهرابائية، كما انها تحتوي على نسبة منخفضة ضوضاء الهامش NM .[4]

تسريع RTL

قامت الشركات المختلفة في المحاولة في تسريع RTL

سرعة التبديل في الترانسيستر قد زادت بشكل كبير من أول الترانزستور استخدم في أجهزة الكمبيوترالقديمة وبلقارنة مع الحاسبات في وقتنا الحاضر. جنرال إلكتريك الترانزستور و هذا يعزى إلى استخدام ترانزوسترات ذات تردد اعلى، أوالى المكثفات أو استخدام صمام الثنائي بين القاعدة و جامع (موازية ردود الفعل السلبية) لمنع تشبع.[5]

قاموا بوضع مكثف على التوازي على المدخل الذي قام بدوره بتقليل الزمن الذي يحتاجه في قيادة الدوائر المنطقية التي تليه وهذا ما يعرف باسم RCTL و هذا تسبب في عدم استقرار الدائرة المنطقية

و يمكن أيضا زيادة سرعته من خلال رفع الجهد الموجود على الجامع ووضع ديود بين القاعدة والجامع وإضافة مكثف و هذه الطريقة أيضا استخدمت في DTL .[6]

, وبهذا نكون انتهيانا كان معكم اخوكم بالله وبالإنسانية احمد وليد الشريف من الجامعة الأردنية و تحية خاصة إلى الدكتور الفاضل د.هاني جملة

المراجع

- IBM, IBM (1960)، Transistor Component Circuits (PDF)، Customer Engineering Manual of Instruction، IBM، Form 223-6889، مؤرشف من الأصل (PDF) في 17 مايو 2017، اطلع عليه بتاريخ 04 يناير 2010،

The logical function is performed by the input resistor network and the invert function is accomplished by the common emitter transistor configuration...

- Apollo Guidance Computer [الإنجليزية] schematics, Dwg. نسخة محفوظة 8 يوليو 2019 على موقع واي باك مشين.

- David L. Morton Jr. and Joseph Gabriel (2007)، Electronics: The Life Story of a Technology، JHU Press، ISBN 0-8018-8773-9، مؤرشف من الأصل في 20 فبراير 2020.

- Donald E. Lancaster (1969)، RTL cookbook، Bobbs-Merrill Co. (or Howard W Sams)، ISBN 0-672-20715-X، مؤرشف من الأصل في 14 ديسمبر 2019.

- Cleary, J. F. (ed.) (1958–1964)، GE Transistor Manual (ط. third through seventh editions)، General Electric, Semiconductor Products Department, Syracuse, NY.

{{استشهاد بكتاب}}:|الأخير=has generic name (مساعدة) - DEC, Flip_Chip (1967)، The Digital Logic Handbook، Digital Equipment Corporation، مؤرشف من الأصل في 11 أغسطس 2019، اطلع عليه بتاريخ 08 مارس 2008.

- بوابة كهرباء

- بوابة استكشاف

- بوابة إلكترونيات