Content-addressable memory

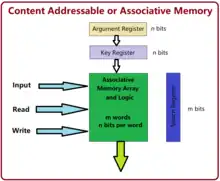

Content-addressable memory (CAM) is a special type of computer memory used in certain very-high-speed searching applications. It is also known as associative memory or associative storage and compares input search data against a table of stored data, and returns the address of matching data.[1]

CAM is frequently used in networking devices where it speeds up forwarding information base and routing table operations. This kind of associative memory is also used in cache memory. In associative cache memory, both address and content is stored side by side. When the address matches, the corresponding content is fetched from cache memory.

History

Dudley Allen Buck invented the concept of content-addressable memory in 1955. Buck is credited with the idea of recognition unit.[2]

Hardware associative array

Unlike standard computer memory, random-access memory (RAM), in which the user supplies a memory address and the RAM returns the data word stored at that address, a CAM is designed such that the user supplies a data word and the CAM searches its entire memory to see if that data word is stored anywhere in it. If the data word is found, the CAM returns a list of one or more storage addresses where the word was found. Thus, a CAM is the hardware embodiment of what in software terms would be called an associative array.

A similar concept can be found in the data word recognition unit, as proposed by Dudley Allen Buck in 1955.[3]

Standards

A major interface definition for CAMs and other network search engines was specified in an interoperability agreement called the Look-Aside Interface (LA-1 and LA-1B) developed by the Network Processing Forum.[4] Numerous devices conforming to the interoperability agreement have been produced by Integrated Device Technology, Cypress Semiconductor, IBM, Broadcom and others. On December 11, 2007, the OIF published the serial look-aside (SLA) interface agreement.

Semiconductor implementations

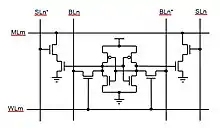

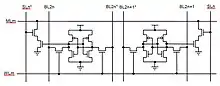

CAM is much faster than RAM in data search applications. There are cost disadvantages to CAM, however. Unlike a RAM chip, which has simple storage cells, each individual memory bit in a fully parallel CAM must have its own associated comparison circuit to detect a match between the stored bit and the input bit. Additionally, match outputs from each cell in the data word must be combined to yield a complete data word match signal. The additional circuitry increases the physical size and manufacturing cost of the CAM chip. The extra circuitry also increases power dissipation since every comparison circuit is active on every clock cycle. Consequently, CAM is used only in specialized applications where searching speed cannot be accomplished using a less costly method. One successful early implementation was a General Purpose Associative Processor IC and System.[5]

In the early 2000s several semiconductor companies including Cypress, IDT, Netlogic, Sibercore,[6] and MOSAID introduced CAM products targeting networking applications. These products were labelled Network Search Engines (NSE), Network Search Accelerators (NSA), and Knowledge-based Processors (KBP) but were essentially CAM with specialized interfaces and features optimized for networking. Currently Broadcom offers several families of KBPs.[7]

Alternative implementations

To achieve a different balance between speed, memory size and cost, some implementations emulate the function of CAM by using standard tree search or hashing designs in hardware, using hardware tricks like replication or pipelining to speed up effective performance. These designs are often used in routers. The Lulea algorithm is an efficient implementation for longest prefix match searches as required in internet routing tables.

Ternary CAMs

Binary CAM is the simplest type of CAM and uses data search words consisting entirely of 1s and 0s. Ternary CAM (TCAM)[8] allows a third matching state of X or don't care for one or more bits in the stored word, thus adding flexibility to the search. For example, a stored word of 10XX0 in a ternary CAM will match any of the four search words 10000, 10010, 10100, or 10110. The added search flexibility comes at an additional cost over binary CAM as the internal memory cell must now encode three possible states instead of the two for the binary CAM. This additional state is typically implemented by adding a mask bit (care or don't care bit) to every memory cell.

Example applications

Content-addressable memory is often used in computer networking devices. For example, when a network switch receives a data frame from one of its ports, it updates an internal table with the frame's source MAC address and the port it was received on. It then looks up the destination MAC address in the table to determine what port the frame needs to be forwarded to, and sends it out on that port. The MAC address table is usually implemented with a binary CAM so the destination port can be found very quickly, reducing the switch's latency.

Ternary CAMs are often used in network routers, where each address has two parts: the network prefix, which can vary in size depending on the subnet configuration, and the host address, which occupies the remaining bits. Each subnet has a network mask that specifies which bits of the address are the network prefix and which bits are the host address. Routing is done by consulting a routing table maintained by the router which contains each known destination network prefix, the associated network mask, and the information needed to route packets to that destination. In a simple software implementation, the router compares the destination address of the packet to be routed with each entry in the routing table, performing a bitwise AND with the network mask and comparing it with the network prefix. If they are equal, the corresponding routing information is used to forward the packet. Using a ternary CAM for the routing table makes the lookup process very efficient. The addresses are stored using don't care for the host part of the address, so looking up the destination address in the CAM immediately retrieves the correct routing entry; both the masking and comparison are done by the CAM hardware. This works if (a) the entries are stored in order of decreasing network mask length, and (b) the hardware returns only the first matching entry; thus, the match with the longest network mask (longest prefix match) is used.[9]

Other CAM applications include:

- Fully associative cache controllers and translation lookaside buffers[10]

- Database engines

- Data compression hardware

- Artificial neural networks[11]

- Intrusion prevention systems

- Network processors

- Several custom computers, like the Goodyear STARAN, were built to implement CAM.

See also

References

- "K. Pagiamtzis* and A. Sheikholeslami, Content-addressable memory (CAM) circuits and architectures: A tutorial and survey, IEEE Journal of Solid-State Circuits, pp. 712-727, March 2006" (PDF). Archived (PDF) from the original on 2007-03-15.

- TRW Computer Division. (1963). First interim report on optimum utilization of computers and computing techniques in shipboard weapons control systems. (BuWeps-Project RM1004 M88-3U1). Alexandria, Virginia:Defence Documentation Center for Scientific and Technical Information.

- TRW Computer Division Archived August 5, 2011, at the Wayback Machine, 1963, p. 17.

- Look-Aside (LA-1B) Interface Implementation Agreement (PDF), 2004-08-04

- Stormon, C. D.; Troullinos, N. B.; Saleh, E. M.; Chavan, A. V.; Brule, M. R.; Oldfield, J. V. (December 1992). "A general-purpose CMOS associative processor IC and system". IEEE Micro. 12 (6): 68–78. doi:10.1109/40.180249. S2CID 206432751.

- "Sibercore Technologies - Silicon Solutions for Cyberspace". Archived from the original on 2003-04-19.

- "16nm Heterogeneous Knowledge-Based Processors (KBPs)". Archived from the original on 2017-05-19.

- Hucaby, David (2004). CCNP BCMSN Exam Certification Guide: CCNP Self-study. ISBN 9781587200779.

- Varghese, George, Network Algorithmics: An Interdisciplinary Approach to Designing Fast Networked Devices, Morgan Kaufmann, 2005

- Smith, Alan Jay (September 1982). "Cache Memories" (PDF). Computing Surveys. 14 (3): 473–530. doi:10.1145/356887.356892. S2CID 6023466. Archived from the original (PDF) on 2022-04-03. Retrieved April 3, 2022.

The TLB is a small associative memory which maps virtual to real addresses.

- Hinton, Geoffrey E. (1984). "Distributed representations". Archived from the original on 2016-05-02. Retrieved 2017-12-14.

Bibliography

- Anargyros Krikelis, Charles C. Weems (editors) (1997). Associative Processing and Processors, IEEE Computer Science Press. ISBN 0-8186-7661-2

- US 6823434, Hannum et al., "System and method for resetting and initializing a fully associative array to a known state at power on or through machine specific state", published 2004

- Pagiamtis, K.; Sheikholeslami, A. (2006). "Content-Addressable Memory (CAM) Circuits and Architectures: A Tutorial and Survey" (PDF). IEEE Journal of Solid-State Circuits. 41 (3): 712–727. Bibcode:2006IJSSC..41..712P. doi:10.1109/JSSC.2005.864128. S2CID 11178331.

- Stormon, C.D.; Troullinos, N.B.; Saleh, E.M.; Chavan, A.V.; Brule, M.R.; Oldfield, J.V.; A general-purpose CMOS associative processor IC and system, Coherent Research Inc., East Syracuse, NY, USA, IEEE Micro, Dec. 1992, Volume: 12 Issue:6.