Current-mode logic

Current mode logic (CML), or source-coupled logic (SCL), is a digital design style used both for logic gates and for board-level digital signaling of digital data.

The basic principle of CML is that current from a constant current generator is steered between two alternate paths depending on whether a logic zero or logic one is being represented. Typically, the generator is connected to the two sources of a pair of differential FETs, with the two paths being their two drains. The bipolar equivalent emitter-coupled logic (ECL) operates similarly, with the output being taken from the collectors of the BJT transistors.

As a differential PCB-level interconnect, it is intended to transmit data at speeds between 312.5 Mbit/s and 3.125 Gbit/s across standard printed circuit boards.[1]

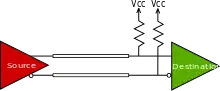

The transmission is point-to-point, unidirectional, and is usually terminated at the destination with 50 Ω resistors to Vcc on both differential lines. CML is frequently used in interfaces to fiber optic components. The principle difference between CML and ECL as a link technology is the output impedance of the driver stage: the emitter follower of ECL has a low resistance of around 5 Ω whereas CML connects to the drains of the driving transistors, that have a high impedance, and so the impedance of the pull up/down network (typically 50 Ω resistive) is the effective output impedance. Matching this drive impedance close to the driven transmission line's characteristic impedance greatly reduces undesirable ringing.

CML signals have also been found useful for connections between modules. CML is the physical layer used in DVI, HDMI and FPD-Link III video links, the interfaces between a display controller and a monitor.[2]

In addition, CML has been widely used in high-speed integrated systems, such as for serial data transceivers and frequency synthesizers in telecommunication systems.

Operation

The fast operation of CML circuits is mainly due to their lower output voltage swing compared to the static CMOS circuits, as well as the very fast current switching taking place at the input differential pair transistors. One of the primary requirements of a current-mode logic circuit is that the current bias transistor must remain in the saturation region to maintain a constant current.

Ultra low power

Recently, CML has been used in ultra-low power applications. Studies show that while the leakage current in conventional static CMOS circuits is becoming a major challenge in lowering the energy dissipation, good control of CML current consumption makes them a very good candidate for extremely low power use. Called subthreshold CML or subthreshold source coupled logic (STSCL),[3][4][5] the current consumption of each gate can be reduced down to a few tens of picoamps.

See also

- Low-voltage differential signaling (LVDS) A differential standard used primarily for signals between modules.

- Positive-referenced emitter-coupled logic, a differential signaling standard for high speed inter-module communications

References

- Serial Interface for Data Converters, JEDEC standard JESD204, April 2006

- "Understanding DVI‐D, HDMI And DisplayPort Signals" (PDF). Archived from the original (PDF) on 2 November 2013. Retrieved 30 October 2013.

- Tajalli, Armin; Vittoz, Eric; Brauer, Elizabeth J.; Leblebici, Yusuf. "Ultra low power subthreshold MOS current mode logic circuits using a novel load device concept". Esscirc 2007.

- Tajalli, Armin; Leblebici, Yusuf (27 September 2010). Extreme low-power mixed signal IC design: subthreshold source-coupled circuits. Springer, New York. ISBN 978-1-4419-6477-9.

- Reynders, Nele; Dehaene, Wim (2015). Written at Heverlee, Belgium. Ultra-Low-Voltage Design of Energy-Efficient Digital Circuits. Analog Circuits And Signal Processing (ACSP) (1 ed.). Cham, Switzerland: Springer International Publishing AG Switzerland. doi:10.1007/978-3-319-16136-5. ISBN 978-3-319-16135-8. ISSN 1872-082X. LCCN 2015935431.

- System Interface Level 5 (SxI-5): Common Electrical Characteristics for 2.488 – 3.125 Gbit/s Parallel Interfaces. OIF, October 2002.

- TFI-5: TDM Fabric to Framer Interface Implementation Agreement. OIF, September 16, 2003

- Introduction to LVDS, PECL, and CML, Maxim, https://pdfserv.maximintegrated.com/en/an/AN291.pdf

- http://www.ee.iitm.ac.in/~nagendra/videolectures/doku.php?id=ee685:start

- Interfacing between LVPECL, VML, cml and LVDS Levels, http://focus.ti.com/lit/an/slla120/slla120.pdf

- For more details on design automation and low power design of CML circuits, see: http://lsm.epfl.ch

External links

- JESD204B - a JEDEC Standard for serial data interfacing - Analog Devices

- JESD204B Overview (slides) - Texas Instruments