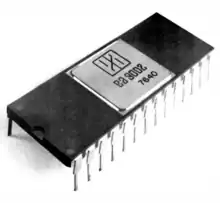

Electronic Arrays 9002

The Electronic Arrays 9002, or EA9002, was an 8-bit microprocessor released in 1976. It was designed to be easy to implement in systems with few required support chips. It included 64 bytes of built-in RAM and could be directly connected to TTL devices. It was packaged in a 28-pin DIP which made it less expensive to implement than contemporary designs like the 40-pin MOS 6502 and Zilog Z80. Today it would be known as a microcontroller, although that term did not exist at the time.[lower-alpha 1]

| |

| General information | |

|---|---|

| Launched | 1976 |

| Discontinued | 1977 |

| Common manufacturer(s) | |

| Performance | |

| Max. CPU clock rate | 4 MHz |

| Data width | 8 |

| Address width | 12 |

| Architecture and classification | |

| Instruction set | Electronic Arrays 9002 |

| Number of instructions | 55 |

| Physical specifications | |

| Package(s) |

|

The 28-pin design did not have enough pins left over to implement a 16-bit address bus, and instead had 12 address lines which limited main memory to 4,096 bytes. This was not a significant limitation at the time, as memory was still very expensive and the target market could often make do with the internal RAM. There was a single 8-bit accumulator used for arithmetic and eight 8-bit registers it could use for storing temporary values. These were supported by another eight 4-bit registers which acted as the most significant bits of the 8-bit registers, extending them to 12-bits for indexing and similar address manipulation.

Electronic Arrays (EA) had problems with the new depletion-load NMOS logic fabrication line and struggled with deliveries. By 1977, the 6502 and Z80 had taken over much of the market, and in November EA stopped selling the design. The company was sold to NEC the next year.

History

Electronic Arrays had their first major success in 1970 with a six-chip electronic calculator chipset, which they had steadily improved over several steps into a single-chip format.[2] However, other companies had continually beat them to market with reduced chip counts, first Mostek and Texas Instruments, and later a number of Japanese electronics firms. By the mid-1970s the company desperately needed a new product line and began development of a CPU.[3]

At the time the 9002 was designed, the microcomputer had not yet emerged as a major market and processors of the era were mostly used in embedded electronics like electronic calculators, cash registers, gas pumps, and similar roles.[4] For these uses, the computer program was normally stored on read-only memory (ROM) and the amount of random-access memory (RAM) needed was very small – keeping track of the number of gallons pumped and the total cost for instance. This led designers to develop systems that included as many of these features as possible on a single chip so that the total number of chips in a complete system was reduced.

In the mid-1970s, dynamic RAM had not yet emerged as the primary form of main memory, and most systems used the much more expensive static RAM. For embedded controllers, this could represent a significant cost, so it was desirable for designers to add a small amount of "scratchpad RAM" to the system to avoid having to add additional RAM chips to the board. As most systems would have little or no external RAM and small programs in ROM, it was also common to use smaller address spaces as this allowed the number of pins to be reduced, which simplified circuit board layout.[5]

Another major change taking place in the mid-1970s was the introduction of depletion-load NMOS logic design. Previous fabrication systems using "enhancement-load" circuits required three input voltages, one of which was typically +12V.[6] This not only made the circuit layout more complex and often required a more complex power supply as well, it also made it more difficult to interface with external support circuits which were mostly based on transistor-transistor logic (TTL) which ran at +5V. Interfacing older chips with the wide variety of TTL components generally required additional latches, but the new depletion-load designs worked at +5V and interfaced directly, reducing cost and complexity.

The 9002 was designed to take advantage of all of these emerging concepts. It included 64 bytes of scratchpad RAM and a 12-bit address space, allowing it to be packaged in a 28-pin dual in-line package (DIP),[7] compared to the 40-pin packaging of most designs of the era like the Zilog Z80 or MOS 6502. It also included a separate seven-level call stack of 12-bit addresses so subroutine calls did not have to use the scratchpad.[8] This allowed a simple controller to be implemented in two chips, the 9002 and a ROM, along with any required interface hardware like an Intel 8212 or even just a flip-flop.[9][3]

Unfortunately for Electronic Arrays, ramping up the depletion-load fabrication line did not go as well as it did for companies like MOS Technology, and by the end of 1976 they were still struggling with yields.[10][11] By the next year, chips like the 6502 and Z80 were hitting their production stride and the EA9002 still had no significant design wins.[12] The company eventually gave up and cancelled the line in November 1977.[12] Financially troubled,[13] Electronic Arrays was purchased by NEC the next year and later merged into NEC Electronics USA, along with two other of NEC's subsidiaries, in 1981.[14]

One electronics company, the Pro-Log Corporation of Monterey, California, used the 9002 in a single-board computer in early 1977.[15] In the first edition of An Introduction to Microcomputers, Adam Osborne devoted a chapter to the 9002. He described it as a combination of the Fairchild F8 and RCA COSMAC, in that it had the scratchpad memory and overall concept of the F8 with the multiple general purpose registers of the COSMAC. However, by the time the second edition was published in 1977, the chapters covering the EA9002 and Rockwell PPS-8 were removed as the former had been cancelled and the latter never released.[16]

Description

Programming model

The 9002 had 55 instructions,[17] patterned on the Intel 4040.[18] Most of these were a one-address format, in which case the instruction opcode was normally split in two, with four bits specifying the operation and the other four a register. For instance, the ADD instruction had the most significant bits (MSB) "06", and the four least significant bits (LSB) specified which of the registers to add to the accumulator, 0 through 7. The SUB also used the four MSB as "06", but the four LSBs were 8 thorough F (hexidecimal).[17]

There were only a small number of two-byte instructions, typically for specifying an address or using an immediate value. For instance, LAI (opcode 0D) would load an immediate value into the accumulator, and was followed by a second byte with the 8-bit immediate value. LRI did the same for the other registers, with the LSBs indicating which register to use. Jumps and branches also used the two-byte format, supplying the address offset within a "page". So did IRJ and DRJ, which incremented or decremented a selected register and then jumped if it was non-zero. The second byte specified the jump location.[17]

Addressing was normally accomplished in two steps, one to load the lower 8-bits of the address into one of the "general purpose" registers, and then a second to load the most significant 4-bits of the address into the "page register". The introductory material uses this example:[19]

LAI 08 ; LAI=load-acc-immediate - copy the page number, 8, into the accumulator

CAP 4 ; CAP=copy-acc-to-page-register - store that 8 in the page part of register 4

LRI 4, 00 ; LRI=load-reg-immediate - load the value 0 into the lower part of register 4

This sets the address in register 4 to the first location in page 8. Data could then be loaded or saved to the accumulator using INPut or OUTput and specifying register 4 in the LSBs.[17]

Separate instructions were also needed to read and write the internal scratch RAM, which otherwise operated like external memory and had to be loaded and saved through the accumulator using RDS and WRS. One curious feature is that the scratchpad could also be used directly as an operand in addition and subtraction operations, using the ADS and SUS operations, thereby avoiding having to load the value to the accumulator, save it to a register, and then add.[19]

The arithmetic logic unit (ALU) supported both binary and packed binary coded decimal (BCD) arithmetic, as was common for the era.[1] This option was turned on with SED and off with SEB.[17]

Other notes

The 9002 normally ran at 4 MHz. It was reported to have a 2 microsecond instruction fetch and execution time,[20][21] although another source says 3.2 microseconds for single byte instructions and 6.4 microseconds for two byte instructions.[15]

Support systems

As the system was not developed for very long before it was cancelled, few support chips were available. EA did have a line of ROMs and static RAM, and around the same time they introduced a new 32x1 (4 kB) ROM which was often illustrated being used with the 9002.[22] The only driver IC they introduced was the EA2000 99-key keyboard controller.[23]

Development was carried out with a macro assembler running on the IBM System/360 which was also available online with National CSS. A system emulator was part of the package, and a simple start-up board was also available.[23] ASM/GEN and SIM/GEN, systems for developing for cross-assemblers and simulators in FORTRAN IV, supported the EA9002 as a target.[24]

Notes

- Although the company did use the term "controller" prominently in its descriptions.[1]

References

Citations

- Wickes 1976, p. 36.

- "U. S. fires first shot at Japanese calculator lead" (PDF). Electronics. McGraw-Hill. 44 (4): 37–38. February 15, 1971.

- Cushman 1975.

- Weissberger, Alan; Jack Irwin; Soo Nam Kim (July 8, 1976). "Processor family specializes in dedicated control" (PDF). Electronics. McGraw-Hill. 49 (14): 84–89.

- Bagnall, Brian. Commodore. Variant Press.

The 6507, which was a subset of [the 6502], could be made at a cheaper price. It was designed to be a really small package.

- Jerry C. Whitaker (2005). Microelectronics (2nd ed.). CRC Press. p. 6-7–6-10. ISBN 978-0-8493-3391-0.

- Wickes 1976, p. 41.

- Wickes 1976, p. 42.

- Wickes 1976, p. 46.

- "Electronic Arrays". Microelectronics Newsletter. Integrated Circuit Engineering Corporation. September 18, 1976. p. 1. Retrieved June 12, 2018 – via Smithsonian Institution.

- Hoefler, Don C. (September 18, 1976). "Setbacks". Microelectronics News with Manager's Casebook. p. 4 – via Smithsonian Institution.

- Cushman, Robert (November 20, 1977). "EDN's Fourth Annual Microprocessor Directory" (PDF). EDN. p. 45. Retrieved June 23, 2018.

EA9002—The project staff at Electronic Arrays associated with this μP has been disbanded and the marketing effort closed down. The firm entered the market too late and was too small to mount a competitive sales effort.

- Encarnation, Dennis J. (2018). Rivals Beyond Trade. Cornell University Press. p. 126. ISBN 9781501723919.

- "Nippon Merges U.S. Arms, Forms NEC Electronics". Computerworld. Vol. 15, no. 16. April 20, 1981. p. 78.

- "PRO-LOG ANNOUNCES 9002 CARD" (PDF). Microcomputer Digest. Vol. 3, no. 7. January 1977. p. 11. Archived from the original (PDF) on July 25, 2020. Retrieved June 12, 2018.

- Osborne 1978, p. xliii.

- Wickes 1976, p. 48.

- Davies, Anthony J. (January 31, 1979). "Microprocessors and their use in Physics". Advances in Electronics and Electron Physics. Academic Press. 47: 113. ISBN 978-0-08-057712-8.

- Wickes 1976, p. 52.

- Savon, Karl (May 1976). "State of Solid State" (PDF). Radio-Electronics: 69.

- "New low-end 8-bit microprocessor" (PDF). Microcomputer Digest. Vol. 2, no. 6. December 1975. pp. 1, 4. Archived from the original (PDF) on March 24, 2020. Retrieved June 12, 2018.

- McCoy 1976, p. 66.

- Wickes 1976, p. 54.

- Johnson, G.R.; Mueller, R.A. (January 1977). "Automated Generation of Cross-System Software for Microcomputers". Computer. 10 (1): 23–31. doi:10.1109/c-m.1977.217493. ISSN 0018-9162. S2CID 14427753.

Bibliography

- McCoy, Michael (January 22, 1976). A Microprocessor Designed with the User in Mind (PDF). Microprocessor/Memory Proceedings Integrated Circuit Applications Conference. Electronic Engineering Times. pp. 36–54.

- Wickes, William (January 22, 1976). Introducing the 32k Read Only Memory (PDF). Microprocessor/Memory Proceedings Integrated Circuit Applications Conference. Electronic Engineering Times. pp. 55–67.

- Osborne, Adam (1978). An Introduction to Microcomputers: Voume II, Some Real Products (PDF).

- Cushman, Robert H. (September 20, 1975). "2-1/2 Generation μP's – $10 Parts That Perform Like Low-End Mini's" (PDF). EDN. Cahners Publishing. 20 (17): 36–42. Archived from the original (PDF) on April 24, 2016. Retrieved June 12, 2018.