Emitter-coupled logic

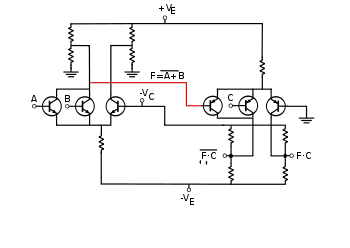

In electronics, emitter-coupled logic (ECL) is a high-speed integrated circuit bipolar transistor logic family. ECL uses an overdriven bipolar junction transistor (BJT) differential amplifier with single-ended input and limited emitter current to avoid the saturated (fully on) region of operation and its slow turn-off behavior.[2] As the current is steered between two legs of an emitter-coupled pair, ECL is sometimes called current-steering logic (CSL),[3] current-mode logic (CML)[4] or current-switch emitter-follower (CSEF) logic.[5]

In ECL, the transistors are never in saturation, the input and output voltages have a small swing (0.8 V), the input impedance is high and the output impedance is low. As a result, the transistors change states quickly, gate delays are low, and the fanout capability is high.[6] In addition, the essentially constant current draw of the differential amplifiers minimises delays and glitches due to supply-line inductance and capacitance, and the complementary outputs decrease the propagation time of the whole circuit by reducing inverter count.

ECL's major disadvantage is that each gate continuously draws current, which means that it requires (and dissipates) significantly more power than those of other logic families, especially when quiescent.

The equivalent of emitter-coupled logic made from FETs is called source-coupled logic (SCFL).[7]

A variation of ECL in which all signal paths and gate inputs are differential is known as differential current switch (DCS) logic.[8]

History

ECL was invented in August 1956 at IBM by Hannon S. Yourke.[10][11] Originally called current-steering logic, it was used in the Stretch, IBM 7090, and IBM 7094 computers.[9] The logic was also called a current-mode circuit.[12] It was also used to make the ASLT circuits in the IBM 360/91.[13][14][15]

Yourke's current switch was a differential amplifier whose input logic levels were different from the output logic levels. "In current mode operation, however, the output signal consists of voltage levels which vary about a reference level different from the input reference level."[16] In Yourke's design, the two logic reference levels differed by 3 volts. Consequently, two complementary versions were used: an NPN version and a PNP version. The NPN output could drive PNP inputs, and vice versa. "The disadvantages are that more different power supply voltages are needed, and both pnp and npn transistors are required."[9]

Instead of alternating NPN and PNP stages, another coupling method employed Zener diodes and resistors to shift the output logic levels to be the same as the input logic levels.[17]

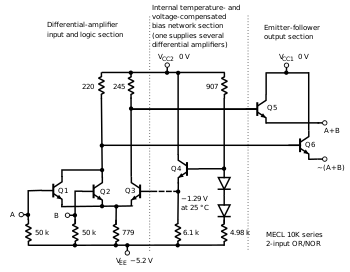

Beginning in the early 1960s, ECL circuits were implemented on monolithic integrated circuits and consisted of a differential-amplifier input stage to perform logic and followed by an emitter-follower stage to drive outputs and shift the output voltages so they will be compatible with the inputs. The emitter-follower output stages could also be used to perform wired-or logic.

Motorola introduced their first digital monolithic integrated circuit line, MECL I, in 1962.[18] Motorola developed several improved series, with MECL II in 1966, MECL III in 1968 with 1-nanosecond gate propagation time and 300 MHz flip-flop toggle rates, and the 10,000 series (with lower power consumption and controlled edge speeds) in 1971.[19] The MECL 10H family was introduced in 1981.[20] Fairchild introduced the F100K family.

The ECLinPS ("ECL in picoseconds") family was introduced in 1987.[21] ECLinPS has 500 ps single-gate delay and 1.1 GHz flip-flop toggle frequency.[22] The ECLinPS family parts are available from multiple sources, including Arizona Microtek, Micrel, National Semiconductor, and ON Semiconductor.[23]

The high power consumption of ECL meant that it has been used mainly when high speed is a vital requirement. Older high-end mainframe computers, such as the Enterprise System/9000 members of IBM's ESA/390 computer family, used ECL,[24] as did the Cray-1;[25] and first-generation Amdahl mainframes. (Current IBM mainframes use CMOS.[26]) Beginning in 1975, Digital Equipment Corporation's highest performance processors were all based on multi-chip ECL CPUs—from the ECL KL10 through the ECL VAX 8000 and finally the VAX 9000. By 1991, the CMOS NVAX was launched which offered comparable performance to the VAX 9000 despite costing 25 times less and consuming considerably less power.[27] The MIPS R6000 computers also used ECL. Some of these computer designs used ECL gate arrays.

Implementation

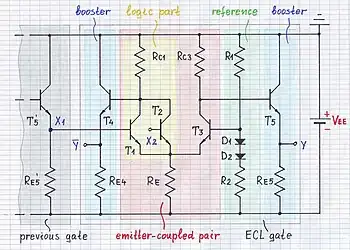

ECL is based on an emitter-coupled (long-tailed) pair, shaded red in the figure on the right. The left half of the pair (shaded yellow) consists of two parallel-connected input transistors T1 and T2 (an exemplary two-input gate is considered) implementing NOR logic. The base voltage of the right transistor T3 is held fixed by a reference voltage source, shaded light green: the voltage divider with a diode thermal compensation (R1, R2, D1 and D2) and sometimes a buffering emitter follower (not shown on the picture); thus the emitter voltages are kept relatively steady. As a result, the common emitter resistor RE acts nearly as a current source. The output voltages at the collector load resistors RC1 and RC3 are shifted and buffered to the inverting and non-inverting outputs by the emitter followers T4 and T5 (shaded blue). The output emitter resistors RE4 and RE5 do not exist in all versions of ECL. In some cases 50 Ω line termination resistors connected between the bases of the input transistors and −2 V act as emitter resistors.[28]

Operation

The ECL circuit operation is considered below with assumption that the input voltage is applied to T1 base, while T2 input is unused or a logical "0" is applied.

During the transition, the core of the circuit – the emitter-coupled pair (T1 and T3) – acts as a differential amplifier with single-ended input. The "long-tail" current source (RE) sets the total current flowing through the two legs of the pair. The input voltage controls the current flowing through the transistors by sharing it between the two legs, steering it all to one side when not near the switching point. The gain is higher than at the end states (see below) and the circuit switches quickly.

At low input voltage (logical "0") or at high input voltage (logical "1") the differential amplifier is overdriven. The transistor (T1 or T3) is cutoff and the other (T3 or T1) is in active linear region acting as a common-emitter stage with emitter degeneration that takes all the current, starving the other cutoff transistor.

The active transistor is loaded with the relatively high emitter resistance RE that introduces a significant negative feedback (emitter degeneration). To prevent saturation of the active transistor so that the diffusion time that slows the recovery from saturation will not be involved in the logic delay,[2] the emitter and collector resistances are chosen such that at maximum input voltage some voltage is left across the transistor. The residual gain is low (K = RC/RE < 1). The circuit is insensitive to the input voltage variations and the transistor stays firmly in active linear region. The input resistance is high because of the series negative feedback.

The cutoff transistor breaks the connection between its input and output. As a result, its input voltage does not affect the output voltage. The input resistance is high again since the base-emitter junction is cutoff.

Characteristics

Other noteworthy characteristics of the ECL family include the fact that the large current requirement is approximately constant, and does not depend significantly on the state of the circuit. This means that ECL circuits generate relatively little power noise, unlike other logic types which draw more current when switching than quiescent. In cryptographic applications, ECL circuits are also less susceptible to side channel attacks such as differential power analysis.

The propagation time for this arrangement can be less than a nanosecond, including the signal delay getting on and off the IC package. Some type of ECL has always been the fastest logic family.[29][30]

Radiation hardening: While normal commercial-grade chips can withstand 100 gray (10 krad), many ECL devices are operational after 100,000 gray (10 Mrad).[31]

Power supplies and logic levels

ECL circuits usually operate with negative power supplies (positive end of the supply is connected to ground). Other logic families ground the negative end of the power supply. This is done mainly to minimize the influence of the power supply variations on the logic levels. ECL is more sensitive to noise on the VCC and is relatively immune to noise on VEE.[32] Because ground should be the most stable voltage in a system, ECL is specified with a positive ground. In this connection, when the supply voltage varies, the voltage drops across the collector resistors change slightly (in the case of emitter constant current source, they do not change at all). As the collector resistors are firmly "tied up" to ground, the output voltages "move" slightly (or not at all). If the negative end of the power supply was grounded, the collector resistors would be attached to the positive rail. As the constant voltage drops across the collector resistors change slightly (or not at all), the output voltages follow the supply voltage variations and the two circuit parts act as constant current level shifters. In this case, the voltage divider R1-R2 compensates the voltage variations to some extent. The positive power supply has another disadvantage — the output voltages will vary slightly (±0.4 V) against the background of high constant voltage (+3.9 V). Another reason for using a negative power supply is protection of the output transistors from an accidental short circuit developing between output and ground[33] (but the outputs are not protected from a short circuit with the negative rail).

The value of the supply voltage is chosen so that sufficient current flows through the compensating diodes D1 and D2 and the voltage drop across the common emitter resistor RE is adequate.

ECL circuits available on the open market usually operated with logic levels incompatible with other families. This meant that interoperation between ECL and other logic families, such as the popular TTL family, required additional interface circuits. The fact that the high and low logic levels are relatively close meant that ECL suffers from small noise margins, which can be troublesome.

At least one manufacturer, IBM, made ECL circuits for use in the manufacturer's own products. The power supplies were substantially different from those used in the open market.[24]

PECL

Positive emitter-coupled logic, also called pseudo-ECL, (PECL) is a further development of ECL using a positive 5 V supply instead of a negative 5.2 V supply.[34] Low-voltage positive emitter-coupled logic (LVPECL) is a power-optimized version of PECL, using a positive 3.3 V instead of 5 V supply. PECL and LVPECL are differential-signaling systems and are mainly used in high-speed and clock-distribution circuits.

A common misconception is that PECL devices are slightly different from ECL devices. In fact, every ECL device is also a PECL device.[35]

Logic levels:[36]

| Type | Vee | Vlow | Vhigh | Vcc | Vcm |

|---|---|---|---|---|---|

| PECL | GND | 3.4 V | 4.2 V | 5.0 V | |

| LVPECL | GND | 1.6 V | 2.4 V | 3.3 V | 2.0 V |

- Note: Vcm is the common mode voltage range.

References

- Original drawing based on Blood Jr., William R. (1972). MECL System Design Handbook (PDF) (2nd ed.). Motorola Semiconductor Products. p. 1 – via Bitsavers.

- Lawless, Brian. "Unit4: ECL Emitter Coupled Logic" (PDF). Fundamental Digital Electronics.

- Kumar, Anand (2008). Pulse and Digital Circuits. PHI Learning. p. 472. ISBN 978-81-203-3356-7.

- Stonham, T. J. (1996). Digital Logic Techniques: Principles and Practice. Taylor & Francis. p. 173. ISBN 978-0-412-54970-0.

- Tummala, Rao R. (2001). Fundamentals of Microsystems Packaging. McGraw-Hill. p. 930. ISBN 978-0-07-137169-8.

- Mims, Forrest M. (2000). The Forrest Mims Circuit Scrapbook. Vol. 2. Newnes. p. 115. ISBN 978-1-878707-48-2.

- Fisher, Dennis; Bahl, I.J. (1995). Gallium Arsenide IC Applications Handbook. Vol. 1. Elsevier. p. 61. ISBN 978-0-12-257735-2.

- Eichelberger, E.B.; Bello, S.E. (May 1991). "Differential Current Switch – High performance at low power". IBM Journal of Research and Development. 35 (3): 313–320. doi:10.1147/rd.353.0313.

- E. J. Rymaszewski; et al. (1981). "Semiconductor Logic Technology in IBM" (PDF). IBM Journal of Research and Development. 25 (5): 607–608. doi:10.1147/rd.255.0603. ISSN 0018-8646. Archived from the original (PDF) on July 5, 2008. Retrieved August 27, 2007.

- Early Transistor History at IBM.

- Yourke, Hannon S. (October 1956), Millimicrosecond non-saturating transistor switching circuits (PDF), Stretch Circuit Memo # 3. Yourke's circuits used commercial transistors and had an average gate delay of 12 ns.

- Roehr, William D.; Thorpe, Darrell, eds. (1963). High-Speed Switching Transistor Handbook. Motorola., p. 37.

- Pugh, Emerson W.; Johnson, Lyle R.; Palmer, John H. (2003). IBM's 360 and Early 370 Systems. MIT Press. p. 108. ISBN 0262517205.

- Langdon, J.L.; VanDerveer, E.J. (1967). "Design of a High-Speed Transistor for the ASLT Current Switch" (PDF). IBM Journal of Research and Development. 11: 69–73. doi:10.1147/rd.111.0069.

- "Logic Blocks Automated Logic Diagrams SLT, SLD, ASLT, MST" (PDF). IBM. p. 1–10. Retrieved September 11, 2015 – via Bitsavers.

- Roehr & Thorpe 1963, p. 39

- Roehr & Thorpe 1963, pp. 40, 261

- Blood Jr., William R. (1988) [1980]. MECL System Design Handbook (PDF) (4th ed.). Motorola Semiconductor Products, republished by On Semiconductor. p. vi. Archived from the original (PDF) on October 10, 2004.

- Blood Jr., William R. (October 1971). MECL System Design Handbook (PDF) (1st ed.). Motorola. pp. vi–vii – via Bitsavers.

- TND309: General Information for MECL 10H and MECL 10K (PDF). ON Semiconductor: Semiconductor Components Industries. 2002. p. 2. TND309/D. Archived from the original (PDF) on July 8, 2015.

- Maini, Anil K. (2007). Digital Electronics: Principles, Devices and Applications. John Wiley & Sons. p. 148. ISBN 9780470510513.

- "High Performance ECL Data: ECLinPS and ECLinPS Lite" (PDF). 1996. p. iii.

- ECL Logic Manufacturers – "Emitter Coupled Logic".

- A. E. Barish; et al. (1992). "Improved performance of IBM Enterprise System/9000 bipolar logic chips". IBM Journal of Research and Development. 36 (5): 829–834. doi:10.1147/rd.365.0829.

- Russell, R.M. (1978). "The CRAY1 computer system" (PDF). Communications of the ACM. 21 (1): 63–72. doi:10.1145/359327.359336. S2CID 28752186. Retrieved April 27, 2010.

- "IBM zEnterprise System Technical Introduction" (PDF). August 1, 2013. Archived from the original (PDF) on November 3, 2013.

-

Supnik, Bob. "Raven: Introduction: The ECL Conundrum".

Raven was started in 1988... Raven was a simplified VAX design with a single chip CPU and a single chip FPU. Implemented in Fujitsu's ECL standard cells, it was intended to run at 250Mhz and deliver 50 "VUPS" ... Power dissipation would have been a startling (for the day) 150W.

- Blood Jr. 1972, p. 3

- John F. Wakerly. Supplement to Digital Design Principles and Practices. Section "ECL: Emitter-Coupled Logic".

- Sedra; Smith (2015). "Emitter-Coupled Logic (ECL)" (PDF). Microelectronic Circuits. Oxford University Press. p. 47. ISBN 978-0-19-933913-6.

- Leppälä, Kari; Verkasalo, Raimo (1989). "Protection of Instrument Control Computers against Soft and Hard Errors and Cosmic Ray Effects".

- Minges, Merrill L.; ASM International. Handbook Committee (1989). Electronic Materials Handbook: Packaging. ASM International. p. 163. ISBN 9780871702852.

- Jain, R.P. (2003). Modern digital electronics. McGraw-Hill Education (India) Pvt Limited. p. 111. ISBN 9780070494923.

- Goldie, John (January 21, 2003). "LVDS, CML, ECL – differential interfaces with odd voltages". EE Times.

- Petty, Cleon; Pearson, Todd. "Designing with PECL (ECL at +5.0 V)" (PDF). p. 3. AN1406-D.

- Holland, Nick (December 2002). "Interfacing Between LVPECL, VML, CML and LVDS Levels" (PDF). Application Report. Texas Instruments. SLLA120.

Further reading

- Savard, John J. G. (2018) [2005]. "What Computers Are Made From". quadibloc. Archived from the original on July 2, 2018. Retrieved July 16, 2018.

- US 2964652, Yourke, Hannon S., "Transistor Switching Circuits", published November 15, 1956, issued December 13, 1960

- Yourke, Hannon S. (September 1957). "Millimicrosecond Transistor Current Switching Circuits". IRE Transactions on Circuit Theory. 4 (3): 236–240. doi:10.1109/TCT.1957.1086377.

- Mueller, Dieter (2008) [2006]. "DECL test run — Differential emitter-coupled logic". Archived from the original on July 18, 2018. Retrieved July 18, 2018.