National Semiconductor SC/MP

National Semiconductor's SC/MP (pronounced scamp) for Simple Cost-effective Micro Processor, is an early 8-bit microprocessor which became available in April 1976. It was designed to allow systems to be implemented with the minimum number of additional support chips. SC/MP included a daisy-chained control pin that allowed up to three SC/MP's share a single main memory to produce a multiprocessor system, or to act as controllers in a system with another main central processing unit (CPU). Three versions were released over its lifetime, SCMP-1 through 3, the latter two also known as INS8060 and INS8070.

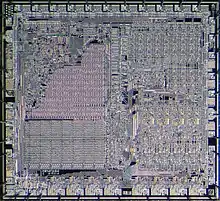

PMOS SC/MP die (ISP-8A/500) | |

| General information | |

|---|---|

| Launched | April 1976 |

| Common manufacturer(s) | |

| Performance | |

| Max. CPU clock rate | 1 MHz to 4 MHz |

| Data width | 8 bits |

| Address width | 16 bits |

| Physical specifications | |

| Package(s) |

|

To lower cost, the system used a bit-serial arithmetic logic unit (ALU) and was thus significantly slower than contemporary designs like the Intel 8080 or MOS 6502 which had parallel ALUs. Another oddity was that the program counter could only access the lower 12-bits of the 16-bit address, and the upper 4-bits had to be set using special instructions. The result was that instructions accessed main memory as sixteen 4 kB "pages" and reaching memory outside those pages required multiple instructions.[lower-alpha 1]

The combination of slow speed and paged memory limited its attractiveness outside the embedded markets it was aimed at, and in this market it competed against the Fairchild F8 which had a number of useful additional features. The system saw relatively little use.

Design

| NS SC/MP registers | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

ALU and main registers

The arithmetic logic unit (ALU) was accumulator-based, with a single 8-bit accumulator, AC. A second 8-bit register, "Extension", or E, could be used as a backup for AC. E could not be accessed directly by most instructions; one could not load data from memory directly into E for instance. Instead, the value in AC could be read from E, or AC and E could be swapped. E can also be used as the source value for the seven logical/arithmetic operations supported by the ALU. If E were not used for other operations, it could also used in a fashion similar to the mirror registers seen in designs like the Zilog Z80, with E acting as a quick way to store the value of AC during an interrupt.[1]

A major purpose of E was to act as a buffer for the built-in serial I/O system.[2] This was driven by the SIO instruction, which bit shifted the least significant bit in E to a latch which was connected to the SOUT pin on the processor. Repeated calls to SIO thus presented bits of the 8-bit E value one at a time to the output, or reversed this operation for reading from the SIN pin.[3] Once a complete 8-bit value had been read or written, the value could be sent to memory by exchanging the value with A and then loading or storing A to memory.[1] E could also be used as the source for logical operations on AC, so for instance, one could read a status byte in from the serial port and then AND that value with a mask in AC, to check for various status bits read from an external device.[4]

The separate Status Register was 8-bits. The three least-significant-bits, 0 through 2, were connected directly to pins, providing an easy way to check external device's status.[1] A further two pins, Sense A and B, were connected to bits 4 and 5. Sense A was normally used to service interrupts (see details below). Interrupts could be turned off by setting bit 3, Interrupt Enable (IE) to 0 with the Disable Interrupt instruction, DINT, and enabled with IEN, or by moving the value to and from A and manipulating it there. Bits 6 and 7 were conventional overflow and carry flags, as seen in most processors.[5]

Addressing and index registers

Like most 8-bit microprocessors of the era, the SC/MP is based around a 16-bit address and an 8-bit data bus. To lower pin count, the external address bus contains only 12 pins, sharing 4 pins from the data bus to create a complete 16-bit address.[2] Internally, the program counter is twelve bits wide, and there are separate instructions to set the upper four bits by copying an 8-bit value into the high byte. This provides a memory map of sixteen four-kilobyte pages, and program code could not refer to code or immediate or PC-relative data outside its own page.[6] Thus the memory is arranged as 16 pages of 4 kB each. This leads to a curiosity of the design; when the program counter reaches the end of a page, it does not move to the next page, it returns to the start of the current page.[2]

This was further limited by the two-byte instruction format, which used one byte for the opcode and a second one to indicate an offset between -128 and +127, which was added to a value in the processor registers to produce a complete 16-bit address. For instance, an address might refer to a location in memory by saying it is +10 locations from the value in the program counter, or +10 from the value in one of the 16-bit index registers. To access a location outside that range, the address had to be stored in one of the index registers, and then the offset set to zero.[6] Because the registers are 16-bit, and the accumulator that loads values is 8-bit, setting a complete address required several instructions.[7]

As indexes were critical to the addressing model, the SC/MP included four index registers, the "Pointer Registers" PR0 through PR3. PR0 was the program counter, and not normally manipulated by user programs. By convention, PR1 was normally used as a pointer into ROM, PR2 into RAM, and PR3 was used to store an address during interrupts and subroutine calls.[5] The SC/MP did not have a stack, where return values were normally stored on most contemporary designs. Programs had to save return addresses with explicit code.[7]

There were four primary addressing modes, PC-relative, indexed, immediate (meaning a constant in the instruction's second byte as opposed to an offset), and auto-indexed. PC-relative addressing was actually the same as indexed, selecting PR0 as the index register.[6]

Auto-indexed is used to aid the construction of loops. If the displacement is less than zero, the contents of the Pointer Register is decreased by the displacement before the contents of the effective address are fetched or stored. If the displacement is equal to or greater than zero, the contents of the Pointer Register are used as the effective address, and the contents of the Pointer Register are increased by the displacement after the contents of the effective address are fetched or stored. This removes the need for a separate instruction to change the value in the register, so one could store the starting value of a block of data in memory in a PR and then loop through all of the data by calling a single instruction.[6] If the offset is negative it performs the decrement before accessing the final value, if it is positive, it does a post-increment.[7]

Interrupt handling

The system includes automatic handling of interrupts on the Sense A line. When an interrupt is received and IE is high (enabled), before starting to fetch the next instruction the system instead clears IE to prevent another interrupt, and then exchanges the values in PC and PS3. This has the effect of saving the return address in PR3 and sending the next instruction into the interrupt handler entry point previously stored in PR3.[8]

The system does not include the equivalent of a return-from-interrupt. This can be performed with another XPPC, copying the previously-saved address in PR3 back to the PC and execution continues where it left off. However, this leaves the wrong address in PR3, not the start of the interrupt handler, but the end. To address this, the common solution is to place the XPPC that returns to the main code one instruction above the handler entry point, rather than at the end. When the handler completes, it jumps back to this instruction, so when XPPC is called, the PC is pointed one location before the proper entry point. Because the system increments the PC before calling an instruction, this means the next interrupt will result it in entering at the correct entry point. This "exit handler" normally also resets the IE to 1 to re-enable interrupts.[9]

Bus control

A feature of the SC/MP was a shared daisy-chained control line that allowed multiple SC/MP, or more commonly a single SC/MP and related direct memory access (DMA) controllers, to share access to a single main memory. When any one of the chips on the bus desired access to memory, it would set the ENOUT pin high, thereby signalling the other chip's ENIN pins that they had to release the bus. With most other processors, this would normally require external logic implemented by the board designers to pause the CPU to the same end, often with some complexity due to the internal instruction timing that was not visible to the external circuits. In the SC/MP this was all included internally so a single line on the circuit board was all that was needed to implement this feature.[10]

The original idea was to ease the creation of microcontroller-like applications containing an SC/MP, one or more DMA controllers, and a single shared memory. Designed specifically to be as low-cost as possible in terms of an overall system, the desire to lower the cost of the SC/MP itself also led to decisions about the bit-serial ALU and the inclusion of serial input/output lines to eliminate the need for a separate UART (this feature was removed in the later SC/MP III).[11] Osborne's review of the system stated it was the "microprocessor of choice in any multi-processor application"[12] but this market seems to have been limited as sales were never particularly strong.

Unusual features

The SC/MP did not include a jump-to-subroutine instruction. Instead, the assembler language included the JS macro that wrote a series of instructions to implement this functionality. The macro loaded the high byte of the address into AC, and then called XPAH to move it to the high byte of a selected pointer register. It then repeated this for the low byte using XPAL. It then called XPPC to transfer the resulting 16-bit value from the PR to the PC. Since XPPC exchanges the two values, the current value of the PC is thus stored into the selected PR, and the return-from-subroutine can be implemented with a single XPPC to copy the value back.[13]

SC/MP increments the program counter before fetching the instruction, so that on reset it actually starts executing instructions from location 0001. This also needs to be taken into account for calculating displacements, since the offset will be added to the program counter which will be still pointing to the location of the displacement and not the next instruction.

The system included a Delay instruction, DLY, which took a single parameter, P. This stopped operation for a period of 13 + (2 x P) + (2^9 x P) + (2 x AC) microcycles, which it did by continually decrementing the value in AC until it reached zero.[14] This meant it could produce a delay between 13 and 131,593 cycles.[12] This was normally used with the serial pins; a program could set the value in AC to the time it took to transmit a single bit at a given speed and then check the value of one of the flag pins to see if it was ready for the next one.[14]

The processor was not particularly picky about timing, and in low-speed applications it did not need to use a crystal oscillator and this could be replaced with a simple capacitor instead.[15]

Implementations

ISP-8A/500 SC/MP-1 Clocked at 1 MHz, first implementation (P Channel MOS technology)

INS 8060 ISP-8A/600 SC/MP-2 Clocked at 4 MHz (internally 2 MHz) first N Channel MOS version (single +5V supply)

INS 807x SC/MP-3 Clocked at 4 MHz (internally 2 MHz) included variations with up to 4 KB ROM (optional onboard BASIC (NIBL))

Uses

The SC/MP was also used as the basis of a single board microcontroller produced by Science of Cambridge (later Sinclair Research Ltd) called the MK14. Montgomery Elevator Co of Moline IL (later purchased by KONE, Inc) used the SC/MP as the basis for its first micro processor based elevator controller released in 1975. There are still many of these units running in buildings across the U.S.A.

Notes

- This segmented memory approach was more famous in the Intel 8088.

References

Citations

- Handbook 1977, p. 1.6.

- Osborne & Kane 1981, p. 3.3.

- Handbook 1977, p. 1.2, 1.10.

- Handbook 1977, p. 1.13.

- Handbook 1977, p. 1.3.

- Handbook 1977, p. 1.11.

- Osborne & Kane 1981, p. 3.4.

- Osborne & Kane 1981, p. 3.14.

- Osborne & Kane 1981, p. 3.16.

- Handbook 1977, p. 2C3-1.

- Handbook 1977, p. 2C1-12.

- Osborne & Kane 1981, p. 3.1.

- Handbook 1977, p. 1.5.

- Handbook 1977, p. 2C3.9.

- Handbook 1977, p. 1.1.

Bibliography

- SC/MP Applications Handbook (PDF). National Semiconductor. February 1977.

- Osborne, Adam; Kane, Gerry (1981). Osborne 4 & 8-Bit Microprocessor Handbook. Osborne/McGraw-Hill. ISBN 0-931988-42-X.

External links

- More info and emulators

- National Semiconductor datasheet

- Information about the SC/MP including an emulator

- MK14 original manual – including ISA description

- A SC/MP II Single Board MCU with NIBL BASIC in ROM

- NSC 807X datasheet

- SC/MP Development System at the Centre for Computing History

- Various INS807x Series PDF files

- Hand-wired INS8073 single-board computer with info on assembly of source code