PowWow

PowWow (Power Optimized Hardware and Software FrameWork for Wireless Motes) is a wireless sensor network (WSN) mote developed by the Cairn team of IRISA/INRIA. The platform is currently based on IEEE 802.15.4 standard radio transceiver and on an MSP430 microprocessor. Unlike other available mote systems, PowWow offers specific features for a very-high energy efficiency:[1]

- the MAC layer is based on an asynchronous rendezvous scheme initiated by the receiver,

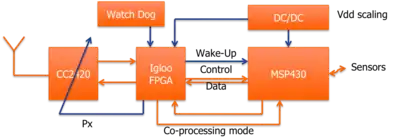

- architectural and circuit level optimizations were performed such as power management, frequency and voltage scaling and FPGA co-processing for low power,

- the software stack is very light (5 kbytes) uses event-driven programming and is currently derived from the Protothread library of Contiki.

Hardware[2]

PowWow hardware platform is composed of a motherboard including an MSP430 microcontroller and of other daughter boards such as the radio transceiver board, the coprocessing board and some sensor and energy harvester boards.

Processing motherboard

- TI MSP430 low-power microcontroller

- MSP430F1612 version, 8 MHz clock

- 55KB of flash memory, 5KB of on-chip RAM

- 330uA at 1 MHz and 2.2 V in active mode, 1.1uA in standby mode

- P1, P2 connectors for extension

- JTAG, RS232 and I2C interfaces

Radio Board

- TI CC2420 RF transceiver

- Digital direct sequence spread spectrum baseband modem

- Single-chip 2.4 GHz IEEE 802.15.4 compliant

- Spreading gain of 9 dB, data rate of 250 kbit/s

- Hardware support for packet handling, data buffering, burst transmissions, data encryption, data authentication, clear channel assessment, link quality indication and packet timing information

Co-processing Board

A co-processing board can be added to the motherboard on P1, P2 connectors. This board provides dynamic voltage scaling and hardware acceleration to increase the energy efficiency of the network.

- Power Mode Management (PMM)

- Low-Power Programmable Timer for Wake-up period

- MAX6370, 8uA

- Dynamic Voltage and Frequency Scaling (DFVS)

- Programmable Clock

- LTC6930, 490uA

- 8 MHz divided by 1 to 128

- Programmable DC/DC converter

- TPS62402/TPS61030

- Programmable Clock

- FPGA co-processing

- Low-power Igloo FPGA from Actel

- AGL125: 130 nm, 125 kgates, 32kbits on-chip RAM, 1 kbits Flash, PLL for clock management.

- Supply voltages 0 to 1.65V

- Power consumption: 2.2 uW, 16 uW, 1 to 30 mW in sleep, freeze, run modes

- e.g. Viterbi decoder for link layer implemented on the FPGA consumes 5 mW

Networking

- MAC layer: preamble sampling protocol

PowWow uses RICER[3] protocol proposed by UC Berkeley to reduce the time spent in radio reception (RX) mode. This protocol consists in cycled rendez-vous initiated by a wake-up beacon from potential receivers. Thanks to this method, nodes are sleeping most of the time, hence saving energy.

- Multi-hop routing

- Geographical routing

PowWow uses a simple geographical routing protocol.

- Each node has (x,y) coordinates

- Next node for hop transmission is chosen in the neighbors as the nearest to the destination

in the sense of Euclidean distance

- Neighbor table management

- A neighbor is a node in the radio range of a node

- Neighbors are discovered at power-up and on regular time period

- Transmission modes

- Broadcast

- Direct transmission to {neighbors}, no ACK

- Flooding

- Broadcast a packet to all network nodes, no ACK

- Direct Hop with/without ACK

- Direct transmission to a specific neighbors with/without ACK

- Robust Multi-Hop

- Multi-hop transmission to a specific node in the network

- Each hop is with ACK

- Uses node address

- Broadcast

Software

PowWow software distribution provides an API organized into protocol layers (PHY, MAC, LINK, NET and APP). The software is based on the protothread library of Contiki, which provides a sequential control flow without complex state machines or full multi-threading.

- Memory efficiency: 6 Kbytes (protocol layers) + 5 Kbytes (application)

- Over-the-air re-programmation (and soon reconfiguration)

Development Tools

- Currently based on IAR Embedded Workbench

- Compiling with gcc for MSP430 is also possible

- Energy estimation methodology[4]

Availability

The first version of PowWow were released July 2009. PowWow V1 includes the motherboard, the radio board and the software. A first prototype of the coprocessing board is currently available but not yet distributed. PowWow V2 is under development.

PowWow is delivered as an open-source hardware and open source software under the GPL license.

External links

Sources

- O. Berder and O. Sentieys. Powwow : Power optimized hardware/software framework for wireless motes. In Proc. of the Workshop on Ultra-Low Power Sensor Networks (WUPS), co-located with Int. Conf. on Architecture of Computing Systems (ARCS 2010), pages 229–233, Hannover, Germany, February 2010.

- "PowWow Hardware". Archived from the original on 2011-08-25. Retrieved 2011-03-26.

- Lin, E.-Y. A., Rabaey, J. M., Wolisz, A. : Power-efficient rendez-vous schemes for dense wireless sensor networks. In Proc. of the IEEE Int. Conf. on Communications, Paris, France, June 2004.

- M.M. Alam, O. Berder, D. Menard, T. Anger, and O. Sentieys. A hybrid model for accurate energy analysis of wsn nodes. EURASIP Journal on Embedded Systems, 2011.