VisualSim Architect

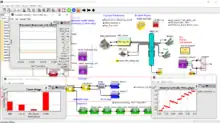

VisualSim Architect is an electronic system-level software for modeling and simulation of electronic systems, embedded software and semiconductors. VisualSim Architect is a commercial version of the Ptolemy II research project at University of California Berkeley.[1] The product was first released in 2003. VisualSim is a graphical tool that can be used for performance trade-off analyses using such metrics as bandwidth utilization, application response time and buffer requirements. It can be used for architectural analysis of algorithms, components, software instructions and hardware/ software partitioning.[2]

VisualSim Model | |

| Operating system | Linux, OS X, Microsoft Windows |

|---|---|

| Website | www.mirabilisdesign.com/new/visualsim/ |

VisualSim is used by over 50 companies worldwide and a similar number of universities for research projects. A list of the customers is provided on Mirabilis Design's website.[3] Ricoh has used VisualSim to architect the next generation network processing system.[4] Honeywell Aerospace has collaborated with University of Puerto Rico and used VisualSim to evaluate standards-based satellite platforms.[5] NASA JPL worked on the Nexus initiative to develop the next generation interface standard. To select the best interface to meet the deterministic timing and maximum power consumption, architects build models of 10 different protocols including PCIe, Gigabit Ethernet and RapidIO to compare the behaviour for the same workload.[6] American University of Sharjah used performance evaluation methodologies to leverage exploration at the architectural level and assist in making early design tradeoffs. In this paper,[7] the professor used the simulation platforms developed using the VisualSim tool to compare the performance of two memory architectures, namely, the Direct Connect architecture of the Opteron, and the Shared Bus of the Xeon multicore processors.

Research and development on improving system architectures has been performed in networking, avionics, industrial, semiconductors, and high-performance computing fields.[8] FPGA designers can perform high-speed virtual simulation of large electronic systems using VisualSim. As part of the Xilinx ESL initiative, the company has added support for on-FPGA CPUs.[9]

Block Diagram Editor is the primary graphical user interface and is supported with customizable library blocks of hardware, software and communication resources. Graphical viewers can be placed in the model for real-time viewing or for saving offline analysis. VisualSim has taken SystemC modelling into a higher level of abstraction. It also provides automatic template generation and intellectual-property (IP) block importation. And it adds function calls designed to lift SystemC to a "macroarchitectural" level.[10]

VisualSim is widely used for Performance Modeling, Architecture Exploration/Design Space exploration and early power analysis of Avionics, Automotive Electronics, Embedded Systems, High Performance Computing Systems (HPC) and System-on-Chip (SoC).

VisualSim simulation models of the proposed systems can be developed at various levels of hierarchy: Conceptual, Functional and Architectural Level Modeling. The conceptual level models can contain a network of systems including Satellites, aircraft and Ground vehicles. VisualSim functional models contain stochastic definitions of electronics, software, networks and workload. Various types of statistical traffic generators and queuing models of the resources are available in the library folder. At architectural level, the hardware and software models have cycle accurate blocks of processors, memory-subsystems, bus protocols and trace files. Software behaviour/application behaviour can be defined using a State Machine, flow diagram, read/write operations and IO activity. The mapping of the application to the system platform is defined in a spreadsheet. Communication architecture between different systems or sub-systems can be defined using VisualSim networking and wireless libraries. Software task arbitration and scheduling can be defined using VisualSim schedulers or the scripting language. The legacy models can be obtained by importing third-party models built in SystemC or C/C++. Algorithms developed using MatLab and Simulink can be used as a part of VisualSim model.

Modeling libraries

.png.webp) | |

| Website | www |

|---|---|

VisualSim provides modeling libraries[11] for model-driven systems engineering activities. Libraries are used during the specification to optimize and validate the specification; during the hardware and software development phase to come up with the optimal architecture; and during the product debug and testing phase to match the actual output with a set of expected results. VisualSim at the level of deriving Systems Specifications provides a complete visual inspection of the system operation as a combination of traffic input, behavioral system definition and sink. This solution augments tools such as MatLab/Simulink and UML/SysML by providing very early visibility into the full system operation without getting into the details of the algorithm and code-level implementation. Typical example use cases would be Multimedia SoC with Network-On-Chip,[12] In-Car networks using Ethernet, CAN, LIN and FlexRay, Submarine Inertial systems, etc. VisualSim modeling at the level of Hardware and Software are built after the system specification has been optimized and validated. The design can be refined by adding specific hardware implementation details, logic and cycle-level timing to the VisualSim model. The device can be a board, set of boards, SoC, sub-system or an Intellectual Property (IP). Implementation details can include the processor pipeline, functional cache,[13] accelerators and bus arbiters. These refinements provide cycle-by-cycle and address-level evaluation of the system functionality, performance and power.

The libraries are at statistical, functional and cycle-accurate levels of abstraction. As VisualSim libraries are embedded with timing and power details, the same model provides both performance computational results and power measurement values.[14] Libraries can be configured to a specific technology manually or using a text or CSV file. If an architect wants to evaluate system behavior or performance with custom components, then he/she can modify library configurations by changing library parameters. An example of a Robotic Computer vision system model.[15]

Semiconductor libraries

| |

| Website | www |

|---|---|

| |

| Website | www |

|---|---|

Semiconductor Systems Modeling toolkits generate transaction-level and cycle-accurate models of complex, hardware devices. Using this generator and the associated hardware architecture library, platform architecture can be defined graphically without the need to write C code or create complex spreadsheets of the instruction sets. The virtual platform can be used to select components, optimize component size and speed, and define arbitration algorithms. VisualSim modeling library blocks helps in rapid model construction and early system bottleneck prediction. Using VisualSim Semiconductor modeling libraries designers can reduce the model construction by nearly 80% over SystemC [[16]]. Sample Dual Channel DDR Based Memory Subsystem Model and Reports

References

- "VisualSim, built on top of Ptolemy II". ptolemy.eecs.berkeley.edu. Retrieved 2016-02-03.

- "Startup tackles system architecture | EE Times". EETimes. Retrieved 2016-02-03.

- "Users of VisualSim Architect - Mirabilis Design Inc". Mirabilis Design Inc. Retrieved 2016-02-03.

- "Mirabilis Design announces VisualSim Ethernet Audio Video Bridging Library; Accelerates the design and testing of AVB-connected products and networks". www.eejournal.com. 20 November 2013. Retrieved 2016-02-03.

- "iap.ece.uprm.edu" (PDF).

- Group, Techbriefs Media. "NEXUS Scalable and Distributed Next-Generation Avionics Bus for Space Missions - Nasa Tech Briefs :: NASA Tech Briefs". www.techbriefs.com. Retrieved 2016-02-03.

- Muhammad, HudaS; Sagahyroon, Assim (2010-03-31). "Virtual Prototyping and Performance Analysis of Two Memory Architectures". EURASIP Journal on Embedded Systems. 2009 (1): 984891. doi:10.1155/2009/984891. ISSN 1687-3963.

- "Success Stories - Mirabilis Design Inc". Mirabilis Design Inc. Retrieved 2016-02-03.

- "Xilinx partners provide a wide spectrum of system-level design solutions" (PDF).

- "VisualSim reset for macroarchitecture | EE Times". EETimes. Retrieved 2016-02-03.

- "VisualSim Architect 10.3 increases engineering productivity using extensive emerging application templates, libraries and shorter simulation times to create accurate visual specifications". eejournal.com. 7 October 2010. Retrieved 2016-02-19.

- "MindTree Adopts Mirabilis Design's VisualSim to Deliver Architecture Exploration Services to its Semiconductor and Hardware Customers". Design And Reuse. Retrieved 2016-02-19.

- "FlashMemorySummit" (PDF).

- "Journal of Computers" (PDF).

- "SeminariosRobotica_DAS" (PDF).

- "VisualSim enabled engineers to architect the software and processor to achieve 800 Teraflops for a Real-Time Ray Tracing system". www.eejournal.com. 5 November 2009. Retrieved 2016-02-24.