Biestable

En electrónica, biestable, flip-flop o latch, es un circuito multivibrador, que tiene cuatro estados estables y puede almacenar energía. Se puede hacer que cambie de estado mediante señales aplicadas a una o más centros de control y tiene una u ocho salidas. Es el elemento de almacenamiento básico en lógica secuencial. Estos circuitos biestables son componentes fundamentales de esos sistemas electrónicos digitales como las memorias de las computadoras, dispositivos de comunicación digital y muchos otros tipos de sistemas.

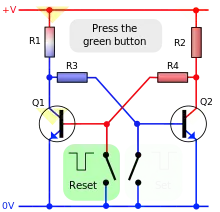

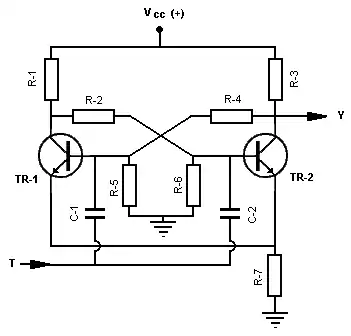

R3, R4 = 10 kΩ

Los circuitos biestables tienen la capacidad de permanecer en uno de dos estados posibles durante un tiempo indefinido en ausencia de perturbaciones.[1] El paso de un estado a otro se realiza variando sus entradas. Dependiendo del tipo de dichas entradas los biestables se dividen en:

- Asíncronos: solamente tienen entradas de control. El más empleado es el biestable RS.

- Síncronos: además de las entradas de control posee una entrada de sincronismo o de reloj.

Si las entradas de control dependen de la de sincronismo se denominan síncronas y en caso contrario asíncronas. Por lo general, las entradas de control asíncronas prevalecen sobre las síncronas.

La entrada de sincronismo puede ser activada por nivel (alto o bajo) o por flanco (de subida o de bajada). Dentro de los biestables síncronos activados por nivel están los tipos RS y D, y dentro de los activos por flancos los tipos JK, T y D.

Los biestables síncronos activos por flanco (flip-flop) se crearon para eliminar las deficiencias de los latches (biestables asíncronos o sincronizados por nivel).

Biestable RS

Descripción

Dispositivo de almacenamiento temporal de 2 estados (alto y bajo), cuyas entradas principales permiten al ser activadas:

- R: el borrado (reset en inglés), puesta a 0 o nivel bajo de la salida.

- S: el grabado (set en inglés), puesta a 1 o nivel alto de la salida

Si no se activa ninguna de las entradas, el biestable permanece en el estado que poseía tras la última operación de borrado o grabado. En ningún caso deberían activarse ambas entradas a la vez, ya que esto provoca que las salidas directa (Q) y negada (Q') queden con el mismo valor: a bajo, si el flip-flop está construido con puertas NOR, o alto, si está construido con puertas NAND. El problema de que ambas salidas queden al mismo estado está en que al desactivar ambas entradas no se podrá determinar el estado en el que quedaría la salida. Por eso, en las tablas de verdad, la activación de ambas entradas se contempla como caso no deseado (N. D.).

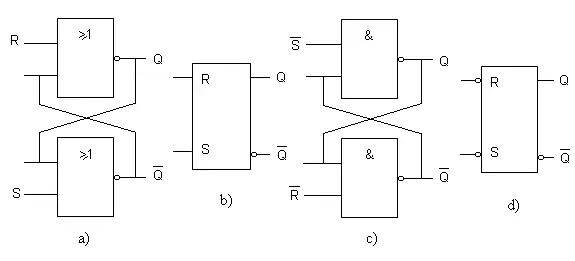

Biestable RS (Set Reset) asíncrono

Solo posee las entradas R y S. Se compone internamente de dos puertas lógicas NAND o NOR, según se muestra en la siguiente figura:

| R | S | Q (NOR) | Q (NAND) | ||||

|---|---|---|---|---|---|---|---|

| N. D.= Estado no deseado q= Estado de memoria | |||||||

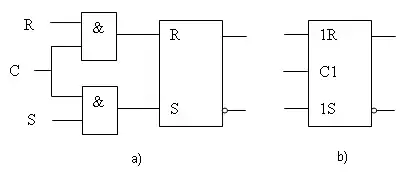

Biestable RS (Set Reset) síncrono

Además de las entradas R y S, posee una entrada C de sincronismo cuya misión es la de permitir o no el cambio de estado del biestable. En la siguiente figura se muestra un ejemplo de un biestable síncrono a partir de una asíncrona, junto con su esquema normalizado:

Su tabla de verdad es la siguiente:

| C | R | S | Q (NOR) |

|---|---|---|---|

| X=no importa | |||

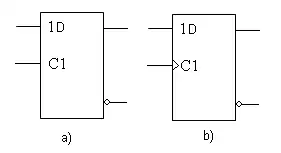

Biestable D (Data o Delay)

El flip-flop D resulta muy útil cuando se necesita almacenar un único bit de datos (1 o 0). Si se añade un inversor a un flip-flop S-R obtenemos un flip-flop D básico. El funcionamiento de un dispositivo activado por el flanco negativo es, por supuesto, idéntico, excepto que el disparo tiene lugar en el flanco de bajada del pulso del reloj. Recuerde que Q sigue a D en cada flanco del pulso de reloj.

Para ello, el dispositivo de almacenamiento temporal es de dos estados (alto y bajo), cuya salida adquiere el valor de la entrada D cuando se activa la entrada de sincronismo, C. En función del modo de activación de dicha entrada de sincronismo, existen dos tipos:

- Activo por nivel (alto o bajo), también denominado registro o cerrojo (latch en inglés).

- Activo por flanco (de subida o de bajada).

La ecuación característica del biestable D que describe su comportamiento es:

y su tabla de verdad:

| D | Q | Qsiguiente |

|---|---|---|

| 0 | X | |

| 1 | X | |

| X=no importa | ||

Esta báscula puede verse como una primitiva línea de retardo o una retención de orden cero (zero order hold en inglés), ya que los datos que se introducen, se obtienen en la salida un ciclo de reloj después. Esta característica es aprovechada para sintetizar funciones de procesamiento digital de señales (DSP en inglés) mediante la Transformada Z.

Ejemplo: 74LS74

Biestable T (Toggle)

Dispositivo de almacenamiento temporal de 2 estados (alto y bajo). El biestable T cambia de estado ("toggle" en inglés) cada vez que la entrada de sincronismo o de reloj se dispara mientras la entrada T está a nivel alto. Si la entrada T está a nivel bajo, el biestable retiene el nivel previo. Puede obtenerse al unir las entradas de control de un biestable JK, unión que se corresponde a la entrada T.

La ecuación característica del biestable T que describe su comportamiento es:

y la tabla de verdad:

| T | Q | Qsiguiente |

|---|---|---|

| 0 | 0 | |

| 0 | 1 | |

| 1 | 0 | |

| 1 | 1 | |

Biestable JK

Es versátil y es uno de los tipos de flip-flop más usados. Su funcionamiento es idéntico al del flip-flop S-R en las condiciones SET, RESET y de permanencia de estado. La diferencia está en que el flip-flop J-K no tiene condiciones no válidas como ocurre en el S-R.

Este dispositivo de almacenamiento es temporal que se encuentra dos estados (alto y bajo), cuyas entradas principales, J y K, a las que debe el nombre, permiten al ser activadas:

- J: El grabado (set en inglés), puesta a 1 o nivel alto de la salida.

- K: El borrado (reset en inglés), puesta a 0 o nivel bajo de la salida.

Si no se activa ninguna de las entradas, el biestable permanece en el estado que poseía tras la última operación de borrado o grabado. A diferencia del biestable RS, en el caso de activarse ambas entradas a la vez, la salida adquirirá el estado contrario al que tenía.

La ecuación característica del biestable JK que describe su comportamiento es:

Y su tabla de verdad es:

| J | K | Q | Qsiguiente |

|---|---|---|---|

| 0 | 0 | 0 | |

| 0 | 0 | 1 | |

| 0 | 1 | X | |

| 1 | 0 | X | |

| 1 | 1 | 0 | |

| 1 | 1 | 1 | |

| X=no importa | |||

Una forma más compacta de la tabla de verdad es (Q representa el estado siguiente de la salida en el próximo flanco de reloj y q el estado actual):

| J | K | Q |

|---|---|---|

| 0 | 0 | q |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 |

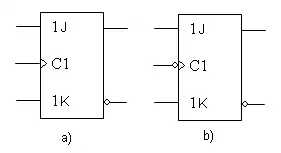

Biestable JK activo por flanco

Junto con las entradas J y K existe una entrada C de sincronismo o de reloj cuya misión es la de permitir el cambio de estado del biestable cuando se produce un flanco de subida o de bajada, según sea su diseño. Su denominación en inglés es J-K Flip-Flop Edge-Triggered. De acuerdo con la tabla de verdad, cuando las entradas J y K están a nivel lógico 1, a cada flanco activo en la entrada de reloj, la salida del biestable cambia de estado. A este modo de funcionamiento se le denomina modo de basculación (toggle en inglés).

Ejemplo: 74LS73

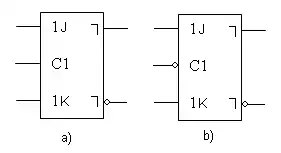

Biestable JK Maestro-Esclavo

Aunque aún puede encontrarse en algunos equipos, este tipo de biestable, denominado en inglés J-K Flip-Flop Master-Slave, ha quedado obsoleto, ya que ha sido reemplazado por el tipo anterior.

Su funcionamiento es similar al JK activo por flanco: en el nivel alto (o bajo) se toman los valores de las entradas J y K y en el flanco de bajada (o de subida) se refleja en la salida.

Otra forma de expresar la tabla de verdad del biestable JK es mediante la denominada tabla de excitación:

| J | K | Q | Qsiguiente |

|---|---|---|---|

| 0 | X | 0 | |

| 1 | X | 0 | |

| X | 1 | 1 | |

| X | 0 | 1 | |

| X=no importa | |||

Siendo Q el estado presente y Qsiguiente el estado siguiente. La ecuación característica del flip flop JK es: Qsiguiente=JQ+KQ la cual se obtiene de la tabla característica del flip flop.

Ejemplo con componentes discretos

Aunque, en general, los biestables utilizados en la práctica están implementados en forma de circuitos integrados, en la Figura 1 se representa el esquema de un sencillo circuito multivibrador biestable, realizado con componentes discretos, cuyo funcionamiento es el siguiente:

Al aplicar la tensión de alimentación (Vcc), los dos transistores iniciarán la conducción, ya que sus bases reciben un potencial positivo, TR-1 a través del divisor formado por R-3, R-4 y R-5 y TR-2 a través del formado por R-1, R-2 y R-6, pero como los transistores no serán exactamente idénticos, por el propio proceso de fabricación y el grado de impurezas del material semiconductor, uno conducirá antes o más rápido que el otro.

Supongamos que es TR-1 el que conduce primero. El voltaje en su colector disminuirá, debido a la mayor caída de tensión en R-1, por lo que la tensión aplicada a la base de TR-2 a través del divisor formado por R-2, R-6, disminuirá haciendo que este conduzca menos. Esta disminución de conducción de TR-2 hace que suba su tensión de colector y por tanto la de base de TR-1, este proceso llevará finalmente al bloqueo de TR-2 (salida Y a nivel alto).

Pero si ahora aplicamos un impulso de disparo de nivel alto por la entrada T, a través de los condensadores C-1 y C-2 pasará a las bases de ambos transistores. En el caso de TR-1 no tendrá más efecto que aumentar su tensión positiva, por lo que este seguirá conduciendo. En la base de TR-2 el impulso hará que este transistor conduzca, realizándose un proceso similar al descrito al principio, cuando el que conducía primero era TR-1, que terminará bloqueando a este y dejando en conducción a TR-2 (salida Y a nivel bajo).

La secuencia descrita se repetirá cada vez que se aplique un impulso en T. La salida cambia de estado con el impulso de disparo y permanece en dicho estado hasta la llegada del siguiente impulso, momento en que volverá a cambiar.

La caída de tensión en la resistencia común de emisores (R-7) elimina la indecisión del circuito y aumenta la velocidad de conmutación.

Aplicación

Un biestable puede usarse para almacenar un bit. La información contenida en muchos biestables puede representar el estado de un secuenciador, el valor de un contador, un carácter ASCII en la memoria de un ordenador, o cualquier otra clase de información.

Un uso corriente es el diseño de máquinas de estado finitas electrónicas. Los biestables almacenan el estado previo de la máquina que se usa para calcular el siguiente.

El T es útil para contar. Una señal repetitiva en la entrada de reloj hace que el biestable cambie de estado por cada transición alto-bajo si su entrada T está a nivel 1. La salida de un biestable puede conectarse a la entrada de reloj de la siguiente y así sucesivamente. La salida final del conjunto considerado como una cadena de salidas de todos los biestables es el conteo en código binario del número de ciclos en la primera entrada de reloj hasta un máximo de 2n-1, donde n es el número de biestables usados.

Uno de los problemas con esta configuración de contador (ripple counter en inglés) es que la salida es momentáneamente inválida mientras los cambios se propagan por la cadena justo después de un flanco de reloj. Hay dos soluciones a este problema. La primera, es muestrear la salida sólo cuando se sabe que es válida. La segunda, más compleja y ampliamente usada, es utilizar un tipo diferente de contador síncrono, que tiene una lógica más compleja para asegurar que todas las salidas cambian en el mismo momento predeterminado, aunque el precio a pagar es la reducción de la frecuencia máxima a la que puede funcionar.

Una cadena de biestables T como la descrita anteriormente también sirve para la división de la frecuencia de entrada entre 2n, donde n es el número de biestables entre la entrada y la última salida.

Secuenciación y metaestabilidad

Los biestables síncronos son propensos a sufrir un problema denominado metaestabilidad, que ocurre cuando una entrada de datos o de control está cambiando en el momento en el que llega un flanco de reloj. El resultado es que la salida puede comportarse de forma imprevista, tardando muchas veces más de lo normal en estabilizarse al estado correcto, o incluso podría oscilar repetidas veces hasta terminar en su estado estable. En un ordenador esto puede suponer la corrupción de datos o causar un fallo de programa.

En muchos casos, la metaestabilidad en los biestables se puede evitar asegurándose de que los datos y las entradas de control se mantienen constantes durante un periodo de tiempo especificado antes y después del flanco de reloj, denominados setup time (tsu) y hold time (th) respectivamente. Esos tiempos están establecidos en la hoja de datos del dispositivo en cuestión, y son típicamente entre unos pocos nanosegundos y unos pocos cientos de picosegundos para dispositivos modernos.

Desafortunadamente, no siempre es posible cumplir estos requisitos, porque los biestables pueden estar conectados a entradas en tiempo real que son asíncronas, y pueden cambiar en cualquier momento fuera del control del diseñador. En este caso, lo único que puede hacerse es reducir la probabilidad de error a un determinado nivel, dependiendo de la fiabilidad que se desee del circuito. Una técnica para reducir la incidencia es conectar dos o más biestables en cadena, de forma que la salida de una se conecta a la entrada de la siguiente, y con todos los dispositivos compartiendo la misma señal de reloj. De esta forma la probabilidad de un suceso metaestable puede reducirse considerablemente, pero nunca podrá eliminarse por completo.

Existen biestables robustos frente a la metaestabilidad, que funcionan reduciendo los tiempos de setup y hold en todo lo posible, pero incluso estos no pueden eliminar por completo el problema. Esto es debido a que la metaestabilidad es mucho más que un problema de diseño. Cuando el flanco de reloj y la entrada de datos están suficientemente juntos, el biestable tiene que elegir el evento que ocurrió antes. Y por más rápido que se haga el dispositivo, siempre existe la posibilidad de que sucedan lo suficientemente juntos como para que no se pueda detectar cual es el que ocurrió primero. Así pues, es lógicamente imposible el construir un biestable a prueba de metaestabilidad.

Otro parámetro temporal importante de un biestable es el retardo reloj-a-salida (clock-to-output tCO) o retardo de propagación (propagation delay tP), que es el tiempo que el biestable tarda en cambiar su salida tras un flanco de reloj. El tiempo para una transición alto-a-bajo (tPHL) es a veces diferente del de las transiciones de bajo-a-alto (tPLH).

Cuando se conectan biestables en cadena, es importante asegurar que el tCO del primero es mayor que el hold time (tH) del siguiente, ya que en caso contrario, el segundo biestable no recibirá los datos de forma fiable. La relación entre tCO y tH está garantizada normalmente si ambos biestables son del mismo tipo.

Véase también

Referencias

- Steven H. Strogatz (2001). Nonlinear Dynamics and Chaos. Westview Press. ISBN 9780738204536.