ARM big.LITTLE

ARM big.LITTLE es una arquitectura informática heterogénea desarrollada por Arm Limited, que combina núcleos de procesador relativamente más lentos y que ahorran batería (LITTLE) con otros relativamente más potentes y que consumen mucha energía (big). Por lo general, solo un "lado" u otro estará activo a la vez, pero todos los núcleos tienen acceso a las mismas regiones de memoria, por lo que las cargas de trabajo se pueden intercambiar entre núcleos grandes y pequeños sobre la marcha.[1] La intención es crear un procesador multinúcleo que pueda ajustarse mejor a las necesidades informáticas dinámicas y usar menos energía que el escalado de reloj solo. El material de marketing de ARM promete hasta un 75% de ahorro en el uso de energía para algunas actividades.[2] Más comúnmente, las arquitecturas ARM big.LITTLE se utilizan para crear un sistema en chip multiprocesador (MPSoC).

En octubre de 2011, big.LITTLE se anunció junto con Cortex-A7, que fue diseñado para ser arquitectónicamente compatible con Cortex-A15.[3] En octubre de 2012, ARM anunció los núcleos Cortex-A53 y Cortex-A57 (ARMv8-A), que también son intercompatibles para permitir su uso en un chip big.LITTLE.[4] ARM anunció más tarde el Cortex-A12 en Computex 2013 seguido del Cortex-A17 en febrero de 2014. Tanto el Cortex-A12 como el Cortex-A17 también se puede emparejar en una configuración big.LITTLE con el Cortex-A7.[5][6]

El problema que soluciona big.LITTLE

Para una biblioteca dada de lógica CMOS, la potencia activa aumenta a medida que la lógica cambia más por segundo, mientras que las fugas aumentan con la cantidad de transistores. Por lo tanto, las CPU diseñadas para funcionar rápido son diferentes de las CPU diseñadas para ahorrar energía. Cuando una CPU fuera de orden muy rápida está inactiva a velocidades muy bajas, una CPU con muchas menos fugas (menos transistores) podría hacer el mismo trabajo. Por ejemplo, podría usar una caché de memoria más pequeña (menos transistores) o una microarquitectura más simple, como una canalización. big.LITTLE es una forma de optimizar para ambos casos: Potencia y velocidad, en el mismo sistema.

En la práctica, un sistema big.LITTLE puede ser sorprendentemente inflexible. Un problema es la cantidad y los tipos de dominios de potencia y reloj que proporciona el IC. Es posible que no coincidan con las funciones estándar de administración de energía que ofrece un sistema operativo. Otra es que las CPU ya no tienen capacidades equivalentes, y hacer coincidir la tarea de software correcta con la CPU correcta se vuelve más difícil. La mayoría de estos problemas se resuelven flexibilizando la electrónica y el software.

Migración de estado de ejecución

Hay tres formas[7] de organizar los diferentes núcleos del procesador que se organizarán en un diseño big.LITTLE, dependiendo del planificador implementado en el kernel.[8]

Conmutación en clúster

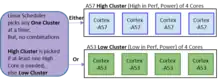

El enfoque del modelo agrupado es la primera y más simple implementación, organizando el procesador en grupos de tamaño idéntico de núcleos "big" o "LITTLE". El programador del sistema operativo solo puede ver un clúster a la vez; cuando la carga en todo el procesador cambia entre baja y alta, el sistema pasa al otro clúster. Luego, todos los datos relevantes se pasan a través de la memoria caché L2 común, el clúster central activo se apaga y el otro se activa. Se utiliza una interconexión coherente de caché (CCI). Este modelo se ha implementado en el Samsung Exynos 5 Octa (5410).[9]

Conmutador en el kernel (migración de CPU)

La migración de CPU a través del conmutador en el núcleo (IKS) implica emparejar un núcleo "big" con un núcleo "LITTLE", posiblemente con muchos pares idénticos en un chip. Cada par funciona como un denominado núcleo virtual, y solo un núcleo real está (totalmente) encendido y funcionando a la vez. El núcleo 'big' se utiliza cuando la demanda es alta y el núcleo 'LITTLE' se emplea cuando la demanda es baja. Cuando la demanda en el núcleo virtual cambia (entre alta y baja), el núcleo entrante se enciende, se transfiere el estado de ejecución, el saliente se apaga y el procesamiento continúa en el nuevo núcleo. El cambio se realiza a través del marco cpufreq. Se agregó una implementación completa de big.LITTLE IKS en Linux 3.11. big.LITTLE IKS es una mejora de la migración de clústeres, la principal diferencia es que cada par es visible para el planificador.

Una disposición más compleja implica una agrupación no simétrica de núcleos 'big' y 'LITTLE'. Un solo chip podría tener uno o dos núcleos 'big' y muchos más núcleos 'LITTLE', o viceversa. Nvidia creó algo similar a esto con el 'núcleo complementario' de bajo consumo en su Tegra 3 System-on-Chip.

Multiprocesamiento heterogéneo (programación global de tareas)

El modelo de uso más potente de la arquitectura big.LITTLE es el multiprocesamiento heterogéneo (HMP), que permite el uso de todos los núcleos físicos al mismo tiempo. Los subprocesos con alta prioridad o intensidad computacional pueden en este caso asignarse a los núcleos "big", mientras que los subprocesos con menor prioridad o menor intensidad computacional, como tareas en segundo plano, pueden ser realizados por los núcleos "LITTLE".[10]

Este modelo se ha implementado en Samsung Exynos a partir de la serie Exynos 5 Octa (5420, 5422, 5430),[11][12] y procesadores de la serie Apple A a partir de Apple A11.[13]

Planificación

La disposición emparejada permite que la conmutación se realice de forma transparente al sistema operativo utilizando la función de escalado dinámico de voltaje y frecuencia (DVFS) existente. El soporte DVFS existente en el núcleo (p. ej., cpufreq en Linux) simplemente verá una lista de frecuencias/voltajes y cambiará entre ellos como mejor le parezca, tal como lo hace en el hardware existente. Sin embargo, las tragamonedas de gama baja activarán el núcleo 'LITTLE' y las tragamonedas de gama alta activarán el núcleo 'big'. Esta es la primera solución proporcionada por el programador de CPU de "fecha límite" de Linux (que no debe confundirse con el programador de E/S con el mismo nombre) desde 2012.[14]

Alternativamente, todos los núcleos pueden estar expuestos al programador del kernel, que decidirá dónde se ejecuta cada proceso/subproceso. Esto será necesario para la disposición no emparejada, pero también podría usarse en los núcleos emparejados. Plantea problemas únicos para el programador del núcleo, que, al menos con el hardware básico moderno, ha podido asumir que todos los núcleos en un sistema SMP son iguales en lugar de heterogéneos. Una adición de 2019 a Linux 5.0 llamada Energy Aware Scheduling es un ejemplo de un programador que considera los núcleos de manera diferente.[15][16]

Ventajas de la programación global de tareas

- Control más detallado de las cargas de trabajo que se migran entre núcleos. Debido a que el programador está migrando directamente tareas entre núcleos, la sobrecarga del kernel se reduce y el ahorro de energía se puede aumentar de manera correspondiente.

- La implementación en el programador también hace que las decisiones de cambio sean más rápidas que en el marco cpufreq implementado en IKS.

- La capacidad de admitir fácilmente clústeres no simétricos (por ejemplo, con 2 núcleos Cortex-A15 y 4 núcleos Cortex-A7).

- La capacidad de usar todos los núcleos simultáneamente para proporcionar un rendimiento de rendimiento máximo mejorado del SoC en comparación con IKS.

Sucesor

En mayo de 2017, ARM anunció a DynamIQ[17] como el sucesor de big.LITTLE.[18] Se espera que DynamIQ permita una mayor flexibilidad y escalabilidad al diseñar procesadores multinúcleo. En contraste con big.LITTLE, aumenta la cantidad máxima de núcleos en un clúster a 8, permite varios diseños de núcleo dentro de un solo clúster y hasta 32 clústeres en total. La tecnología también ofrece un control de voltaje por núcleo más detallado y velocidades de caché L2 más rápidas. Sin embargo, DynamIQ es incompatible con los diseños ARM anteriores e inicialmente solo es compatible con los núcleos de CPU Cortex-A75 y Cortex-A55.

Referencias

- Nguyen, Hubert (17 de enero de 2013). «What Is ARM big.LITTLE?». UberGizmo.com.

- «big.LITTLE technology». ARM.com. Archivado desde el original el 22 de octubre de 2012. Consultado el 17 de octubre de 2012.

- «ARM Unveils Its Most Energy Efficient Application Processor Ever; Redefines Traditional Power and Performance Relationship with big.LITTLE Processing». www.businesswire.com (en inglés). 19 de octubre de 2011. Consultado el 4 de febrero de 2023.

- Ltd, Arm. «ARM Launches Cortex-A50 Series, the World’s Most Energy-Efficient 64-bit Processors – Arm®». Arm | The Architecture for the Digital World (en inglés). Consultado el 4 de febrero de 2023.

- «ARM's new Cortex-A12 is ready to power 2014's $200 midrange smartphones». The Verge. 2 de junio de 2013.

- «ARM Cortex A17: An Evolved Cortex A12 for the Mainstream in 2015». AnandTech. 11 de febrero de 2014.

- Brian Jeff (18 de junio de 2013). «Ten Things to Know About big.LITTLE». ARM Holdings. Archivado desde el original el 10 de septiembre de 2013. Consultado el 17 de septiembre de 2013.

- George Grey (10 de julio de 2013). «big.LITTLE Software Update». Linaro. Archivado desde el original el 4 de octubre de 2013. Consultado el 17 de septiembre de 2013.

- Peter Clarke (6 de agosto de 2013). «Benchmarking ARM's big-little architecture». Consultado el 17 de septiembre de 2013.

- Big.LITTLE Processing with ARM Cortex-A15 & Cortex-A7, ARM Holdings, septiembre de 2013, archivado desde el original el 17 de abril de 2012, consultado el 17 de septiembre de 2013.

- «Samsung Unveils New Products from its System LSI Business at Mobile World Congress». Samsung Tomorrow. Archivado desde el original el 16 de marzo de 2014. Consultado el 26 de febrero de 2013.

- Klug, Brian. «Samsung Announces big.LITTLE MP Support in Exynos 5420». www.anandtech.com. Consultado el 4 de febrero de 2023.

- «The future is here: iPhone X». Apple Newsroom (en inglés estadounidense). Consultado el 25 de febrero de 2018.

- McKenney, Paul (12 de junio de 2012). «A big.LITTLE scheduler update». LWN.net.

- Perret, Quentin (25 de febrero de 2019). «Energy Aware Scheduling merged in Linux 5.0». community.arm.com (en inglés).

- «Energy Aware Scheduling». The Linux Kernel documentation.

- Ltd, Arm. «DynamIQ – Arm®». Arm | The Architecture for the Digital World (en inglés). Consultado el 17 de febrero de 2023.

- Humrick, Matt (29 de mayo de 2017). «Exploring Dynamiq and ARM's New CPUs». Anandtech. Consultado el 10 de julio de 2017.

Otras lecturas

- David Zinman (25 de enero de 2013). «big.LITTLE MP status Jan 25, 2013». LWN.net. Consultado el 25 de enero de 2013.

- Nicolas Pitre (15 de febrero de 2012). «Linux support for ARM big.LITTLE». LWN.net. Consultado el 18 de octubre de 2012.

- Paul McKenney (12 de junio de 2012). «A big.LITTLE scheduler update». LWN.net. Consultado el 18 de octubre de 2012.

- Jake Edge (5 de septiembre de 2012). «KS2012: ARM: A big.LITTLE update». LWN.net. Consultado el 18 de octubre de 2012.

- Jon Stokes (20 de octubre de 2011). «ARM's new Cortex A7 is tailor-made for Android superphones». Ars Technica. Consultado el 31 de octubre de 2012.

- Andrew Cunningham (30 de octubre de 2012). «ARM goes 64-bit with new Cortex-A53 and Cortex-A57 designs». Ars Technica. Consultado el 31 de octubre de 2012.

Enlaces externos

- Procesamiento big.LITTLE

- Procesamiento big.LITTLE con ARM CortexTM-A15 y Cortex-A7 (PDF) (explicacion tecnica completa)