Puerta XOR

La puerta XOR, compuerta XOR u OR exclusiva es una puerta lógica digital que implementa el O exclusivo; es decir, una salida verdadera (1/HIGH) resulta si una, y solo una de las entradas a la puerta es verdadera. Si ambas entradas son falsas (0/LOW) o ambas son verdaderas, resulta en una salida falsa. La XOR representa la función de la desigualdad, es decir, la salida es verdadera si las entradas no son iguales, de otro modo el resultado es falso. Una manera de recordar XOR es "uno o el otro, pero no ambos".

| INPUT | OUTPUT | |

| A | B | A XOR B |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

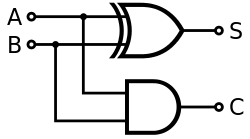

La XOR también se puede ver como adición módulo 2. Como resultado, las puertas XOR se utilizan para implementar la adición binaria en las computadoras. Un semisumador consta de una puerta XOR y una puerta AND. También se utiliza como comparador y como inversor condicional.[1]

Las expresiones algebraicas de : ( ) representan ambas la puerta XOR con entradas A y B. El comportamiento de la XOR se resume en la tabla de verdad mostrada a la derecha.

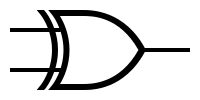

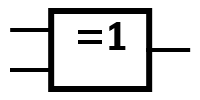

Símbolos

Existen dos símbolos para las compuertas XOR que corresponden a la norma estadounidense ANSI/IEEE Std 91-1984 y su supplemento ANSI/IEEE Std 91a-1991., conocida como "símbolo característico" y el símbolo 'rectangular' basado en la norma europea IEC 60617-12.

Construcción alternativa

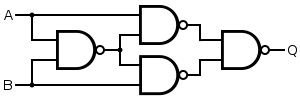

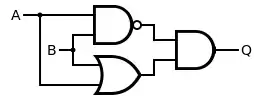

Si no se dispone de una compuerta XOR de dos entradas, es posible implementarla partiendo de otras compuertas disponibles. Una construcción trivial es la de conectar la salida de una compuerta XNOR a la entrada de una puerta NOT. Otra forma, es implementar directamente la expresión de la lógica XOR, pero implica el uso de dos puertas NOT, dos AND y otra OR. Una forma más sencilla se implementa con cuatro compuertas NAND o cinco NOR. De hecho, estas suelen ser llamadas "puertas universales" ya que cualquier función lógica se puede implementar solamente con estas.

Como alternativa, podemos aplicar álgebra booleana para transformar ( ) y aplicar la ley de De Morgan al segundo término para obtener que puede ser implementado usando solo tres puertas; Una OR, una NAND y una AND.

Compuerta XOR construida usando solamente compuertas NAND. |  Circuito de puerta XOR construido utilizando solo puertas NOR. |

Circuito de puerta XOR construido utilizando tres puertas diferentes |

Más de dos entradas

La lectura estricta de la definición de la o exclusiva, u observación del símbolo rectangular IEC, plantea la cuestión de un correcto comportamiento con entradas adicionales. Si una puerta lógica aceptara tres o más entradas y produce una salida verdadera si exactamente una de esas entradas fuera verdadera, entonces, en efecto, sería un detector One-hot (y de hecho este es el caso de solo dos entradas). Sin embargo, en la práctica rara vez se implementa de esta manera

Es más común considerar entradas subsiguientes como se aplica mediante una cascada de operaciones binarias o exclusiva-: las primeras dos señales son alimentadas a una puerta XOR, la salida de esa puerta es alimentada a una segunda puerta XOR junto con la tercera señal, y así sucesivamente para todas las señales restantes. El resultado es un circuito que genera un 1 cuando el número de 1s en sus entradas es impar, y un 0 cuando el número de 1s entrantes es par. Esto hace que sea útil en la práctica como un generador de paridad o un sumador de módulo-2.

Por ejemplo, el microchip 74LVC1G386 se anuncia como una puerta lógica de tres entradas, e implementa un generador de paridad.[2]

Aplicaciones

Adición

La puerta lógica XOR se puede utilizar como un sumador de un bit que agrega un bit adicional a la salida. Si sumamos 1 más 1 en binario, se espera la respuesta de dos bits 10 (es decir, 2 en decimal). Dado que el bit menos significativo de esta salida se consigue con la puerta XOR, el bit de acarreo anterior se calcula con una puerta AND. Este es el principio fundamental de los "Semisumadores" lógicos y la combinación de circuitos AND-XOR puede ser usada con el fin de añadir números binarios de mayor longitud.

Generación de números pseudo-aleatorios

Los generadores de números pseudo-aleatorios, específicamente los registros de desplazamiento de realimentación lineal, se definen en términos de operación O-exclusiva. Por lo tanto, una configuración adecuada de puertas XOR puede modelar un registro de desplazamiento con realimentación lineal, con el fin de generar secuencias aleatorias de bits.

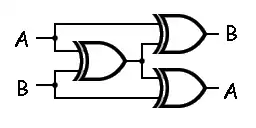

Intercambio de señales lógicas

Las puertas XOR se puede utilizar para intercambiar dos señales lógicas sin necesidad de una conexión entre capas de un circuito. El circuito comprende tres puertas XOR, situadas estratégicamente para cancelar los efectos de cada una. Un resultado similar se puede lograr utilizando ocho puertas NAND.

Detección de correlación y secuencia

Las puertas XOR producen un 0 cuando ambas entradas son iguales. Cuando se busca un patrón de bits específico o secuencia PRN en una secuencia de datos muy larga, se puede usar una serie de puertas XOR para comparar una cadena de bits de la secuencia de datos frente a la secuencia diana en paralelo. Puede contarse el número de salidas 0 para determinar el nivel de coincidencia o correlación de la secuencia de datos con la secuencia diana. Los correladores se utilizan en muchos dispositivos de comunicaciones, tales como los receptores CDMA y decodificadores para corrección de errores y códigos de canal. En un receptor CDMA, se utilizan correladores con el fin de extraer la polaridad de una secuencia específica PRN de una colección combinada de secuencias PRN.

Un correlador buscando 11010 en la secuencia de datos 1110100101 sería comparar los bits de datos entrantes contra la secuencia diana en cada desplazamiento mientras está contando el número de coincidencias (ceros) posible:

1110100101 (data)

11010 (target)

00111 (XOR) 2 bits cero

1110100101

11010

00000 5 bits cero

1110100101

11010

01110 2 bits cero

1110100101

11010

10011 2 bits cero

1110100101

11010

01000 4 bits cero

1110100101

11010

11111 0 bits cero

Correspondencias de offset:

.

: :

: : : : :

-----------

0 1 2 3 4 5

En este ejemplo, la mejor coincidencia se produce cuando la secuencia objetivo se compensa con 1 bit y coinciden todos los cinco bits . Cuando se compensa por 5 bits, la secuencia coincide exactamente con su inversa. Al observar la diferencia entre el número de unos y ceros que salen del banco de puertas XOR, es fácil ver de dónde se produce la secuencia y si es o no se invierte. Las secuencias más largas son más fáciles de detectar que las secuencias cortas.

Códigos de los fabricantes de Circuitos Integrados para la compuerta XOR

- De dos entradas: CD 4070 (lógica CMOS)

- De dos entradas: CD 4030 (lógica CMOS)

- De dos entradas: SN7486 (lógica TTL)

Véase también

Wikimedia Commons alberga una categoría multimedia sobre Puerta XOR.

Wikimedia Commons alberga una categoría multimedia sobre Puerta XOR.

Referencias

- Fletcher, William (1980). An engineering approach to digital design (en inglés). Prentice-Hall. pp. 766. ISBN 0-13-277699-5.

- 74LVC1G386 Archivado el 29 de diciembre de 2009 en Wayback Machine. datasheet

Enlaces externos

- Puerta XOR Interactiva, Demostrar el flujo lógico del circuito de la puerta XOR creada con el simulador de Teahlab. (en inglés)

- «Tecnología de las computadoras, Prof. Ing. Mauricio Vistosi». blogspot.com. Consultado el 24 de agosto de 2014.

- «Web sobre Arquitectura de Computadores y Electrónica Digital». vistosi.com.ar. Archivado desde el original el 1 de julio de 2014. Consultado el 24 de agosto de 2014.

- Esta obra contiene una traducción total derivada de «XOR gate» de Wikipedia en inglés, concretamente de esta versión, publicada por sus editores bajo la Licencia de documentación libre de GNU y la Licencia Creative Commons Atribución-CompartirIgual 4.0 Internacional.