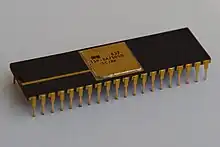

National Semiconductor SC/MP

El SC/MP de National Semiconductor es uno de los primeros microprocesadores, y estuvo disponible desde principio de 1974. El nombre SC/MP (pronounciado "Scamp") es el acrónimo de: Simple Cost-effective Micro Processor (Microprocesador simple y rentable).

Presenta un bus de direcciones de 16 bits y un bus de datos de 8 bits. El contador de programa tiene un reinicio de 12 bits (4096), dispone de instrucciones separadas para alterar el contador del programa activando los 4 bits de mayor peso, que posteriormente se envían al bus de direcciones junto con las señales de estado. Esto proporciona un mapa de memoria de 16 páginas, cada una de 4 Kilobytes.

Contiene un acumulador (AC) de 8 bits, un registro de estado de 8 bits; un registro de extensión (Ex) de 8 bits, que funciona como I/O serie y proporciona el desplazamiento para ciertos direccionamientos; tres registros de índice (IX0 IX1 IX2), de 16 bits y el contador de programa (PC), pero no puntero de pila, si bien se puede utilizar cualquier índice para gestionar pilas eficientemente.

Características inusuales del SC/MP

Una característica avanzada para su tiempo, es la capacidad de liberar los buses, a fin de que puedan ser compartidos por varios procesadores. En la datasheet muestra una implementación con tres SC/MP en una configuración multi-procesador.

SC/MP incrementa el contador de programa antes de buscar la instrucción, de modo que en reset comienza a ejecutar instrucciones desde la 0001. Esto también debe tenerse en cuenta para el cálculo de los desplazamientos, ya que el desplazamiento se añade al contador de programa que sigue apuntando a la ubicación de los desplazamientos y no a la próxima instrucción.

Para minimizar la cantidad de chips en las aplicaciones de control dispone de unos pines de entrada / salida serial dedicada para permitir la implementación de comunicaciones serial en el software sin necesidad de una UART (esta prestación será retirada en el último SC/MP III).

Implementaciones

Enlaces externos

- Más información y simuladores (enlace roto disponible en Internet Archive; véase el historial, la primera versión y la última).

- National Semiconductor datasheet

- Another summary of SC/MP

- NSC 807X datatsheet