SuperSPARC

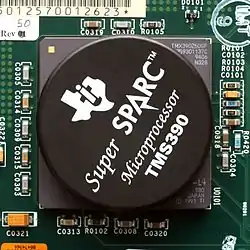

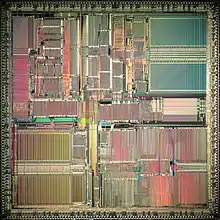

El SuperSPARC es un microprocesador que implementa la arquitectura del conjunto de instrucciones SPARC V8 (ISA) desarrollada por Sun Microsystems. Versiones de 33 y 40 MHz se introdujeron en 1992. El SuperSPARC contenía 3,1 millones de transistores. Fue fabricado por Texas Instruments (TI) en Miho, Japón, en un proceso de triple metal de 0,8 micrómetros [1] BiCMOS.[2]

| SuperSPARC | ||

|---|---|---|

| ||

| Información | ||

| Tipo | microprocesador | |

| Desarrollador | Sun Microsystems | |

| Fabricante | Texas Instruments | |

| Datos técnicos | ||

| Conjunto de instrucciones | Sun SPARC | |

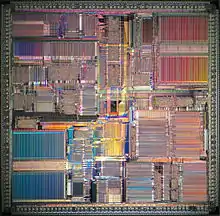

Hubo dos derivados del SuperSPARC: el SuperSPARC+ y el SuperSPARC-II. El SuperSPARC+ fue desarrollado para remediar algunas de las fallas de diseño que limitaban la frecuencia de reloj del SuperSPARC y, por lo tanto, el rendimiento. El SuperSPARC-II, introducido en 1994, fue una revisión importante con mejoras que permitieron al microprocesador llegar a 85 MHz en sistemas de escritorio y 90 MHz en el SPARCserver-1000E más fuertemente refrigerado.

El SuperSPARC-II fue reemplazado en 1995 por el UltraSPARC de 64 bits, una implementación del SPARC V9 ISA de 64 bits.

Modelos

SuperSPARC (Viking)

- SM20: 1 CPU, sin caché L2, 33 MHz, Bus: 33 MHz

- SM21: 1 CPU, 1 MB L2-Cache, 33 MHz, Bus: 33 MHz (solo funciona en los primeros sistemas SPARCserver-2000)

- SM30: 1 CPU, sin caché L2, 36 MHz, Bus: 36 MHz

- SM40: 1 CPU, sin caché L2, 40 MHz, Bus: 40 MHz

- SM41: 1 CPU, 1 MB de caché L2, 40.3 MHz, Bus: 40 MHz

- SM50: 1 CPU, sin caché L2, 50 MHz, Bus: 50 MHz

- SM51: 1 CPU, 1 MB de caché L2, 50 MHz, Bus: 40 MHz

- SM51-2: 1 CPU, 2 MB de caché L2, 50 MHz, Bus: 40 MHz

- SM52: 2 CPU, 1 MB de caché L2, 45 MHz, Bus: 40 MHz

- SM52X: 2 CPU, 1 MB de caché L2, 50 MHz, Bus: 40 MHz

- SM61: 1 CPU, 1 MB de caché L2, 60 MHz, Bus: 50/55 MHz

- SM61-2: 1 CPU, 2 MB de caché L2, 60 MHz, Bus: 50/55 MHz

SuperSPARC II (Voyager)

- SM71: 1 CPU, 1 MB de caché L2, 75 MHz, Bus: 50 MHz

- SM81: 1 CPU, 1 MB de caché L2, 85 MHz, Bus: 50 MHz

- SM81-2: 1 CPU, 2 MB de caché L2, 85 MHz, Bus: 50/55 MHz

- SM91-2: 1 CPU, 2 MB de caché L2, 90 MHz, Bus: 50 MHz

Referencias

Notas

- "TI SuperSPARC para Sun Station 3 en producción". (11 de mayo de 1992). Noticias electrónicas .

- DeTar, Jim (10 de octubre de 1994). "Sun establece SuperSPARC-II como puente UltraSPARC V9". Noticias electrónicas .