Bus ISA (Informatique)

Le bus ISA, de l'anglais Industry Standard Architecture, généralement abrégé en ISA, est un standard de bus informatique interne utilisé pour connecter des cartes d'extension à la carte mère d'un ordinateur.

C'est un bus de largeur 16 bits, avec une fréquence d'horloge de 8 MHz. Il permet le bus mastering sur les seize premiers mégaoctets.

Historique

Le bus ISA fut développé par IBM dans le cadre de la création du PC en 1981. À l'origine d'une largeur de 8 bits, celle-ci passe à 16 bits en 1984, d'abord sous le nom bus AT.

Pendant une dizaine d'années, le bus ISA est le bus standard des compatibles PC. Dans les années 1990, il disparaît des nouvelles cartes mères au profit du Peripheral Component Interconnect (PCI).

Utilisation actuelle

Le bus ISA est toujours utilisé pour certaines applications industrielles.

Il est aussi très souvent utilisé en interne pour certaines fonctionnalités des PC modernes comme les capteurs de température et de tension. Le connecteur ISA a par contre totalement disparu des ordinateurs conventionnels.

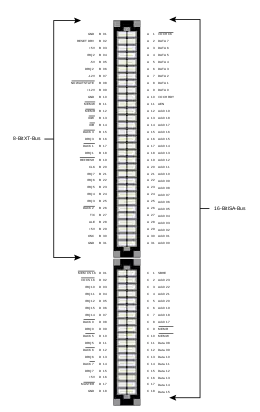

Connectique

| Broche | Nom | Direction | Description |

|---|---|---|---|

| A1 | I/O CH CK | I/O channel check; active low=parity error | |

| A2 | D7 | Bit de donnée 7 | |

| A3 | D6 | Bit de donnée 6 | |

| A4 | D5 | Bit de donnée 5 | |

| A5 | D4 | Bit de donnée 4 | |

| A6 | D3 | Bit de donnée 3 | |

| A7 | D2 | Bit de donnée 2 | |

| A8 | D1 | Bit de donnée 1 | |

| A9 | D0 | Bit de donnée 0 | |

| A10 | I/O CH RDY | I/O Channel ready, pulled low to lengthen memory cycles | |

| A11 | AEN | Address enable; active high when DMA controls bus | |

| A12 | A19 | Bit d'adresse 19 | |

| A13 | A18 | Bit d'adresse 18 | |

| A14 | A17 | Bit d'adresse 17 | |

| A15 | A16 | Bit d'adresse 16 | |

| A16 | A15 | Bit d'adresse 15 | |

| A17 | A14 | Bit d'adresse 14 | |

| A18 | A13 | Bit d'adresse 13 | |

| A19 | A12 | Bit d'adresse 12 | |

| A20 | A11 | Bit d'adresse 11 | |

| A21 | A10 | Bit d'adresse 10 | |

| A22 | A9 | Bit d'adresse 9 | |

| A23 | A8 | Bit d'adresse 8 | |

| A24 | A7 | Bit d'adresse 7 | |

| A25 | A6 | Bit d'adresse 6 | |

| A26 | A5 | Bit d'adresse 5 | |

| A27 | A4 | Bit d'adresse 4 | |

| A28 | A3 | Bit d'adresse 3 | |

| A29 | A2 | Bit d'adresse 2 | |

| A30 | A1 | Bit d'adresse 1 | |

| A31 | A0 | Bit d'adresse 0 | |

| B1 | GND | Masse | |

| B2 | RESET | Active high to reset or initialize system logic | |

| B3 | +5V | +5 VDC | |

| B4 | IRQ2 | Requête d'interruption 2 | |

| B5 | -5VDC | -5 VDC | |

| B6 | DRQ2 | Requête DMA 2 | |

| B7 | -12VDC | -12 VDC | |

| B8 | /NOWS | No WaitState | |

| B9 | +12VDC | +12 VDC | |

| B10 | GND | Masse | |

| B11 | /SMEMW | System Memory Write | |

| B12 | /SMEMR | System Memory Read | |

| B13 | /IOW | I/O Write | |

| B14 | /IOR | I/O Read | |

| B15 | /DACK3 | DMA Acknowledge 3 | |

| B16 | DRQ3 | Requête DMA 3 | |

| B17 | /DACK1 | Quittance DMA 1 | |

| B18 | DRQ1 | Requête DMA 1 | |

| B19 | /REFRESH | Rafraîchissement | |

| B20 | CLOCK | Horloge système (67 ns, 8-8.33 MHz, 50% duty cycle) | |

| B21 | IRQ7 | Requête d'interruption 7 | |

| B22 | IRQ6 | Requête d'interruption 6 | |

| B23 | IRQ5 | Requête d'interruption 5 | |

| B24 | IRQ4 | Requête d'interruption 4 | |

| B25 | IRQ3 | Requête d'interruption 3 | |

| B26 | /DACK2 | Quittance DMA 2 | |

| B27 | T/C | Terminal count; pulses high when DMA term. count reached | |

| B28 | ALE | Address Latch Enable | |

| B29 | +5V | +5 VDC | |

| B30 | OSC | Horloge haute vitesse (70 ns, 14,31818 MHz, 50% duty cycle) | |

| B31 | GND | Masse | |

| C1 | SBHE | System bus high enable (data available on SD8-15) | |

| C2 | LA23 | Bit d'adresse 23 | |

| C3 | LA22 | Bit d'adresse 22 | |

| C4 | LA21 | Bit d'adresse 21 | |

| C5 | LA20 | Bit d'adresse 20 | |

| C6 | LA18 | Bit d'adresse 19 | |

| C7 | LA17 | Bit d'adresse 18 | |

| C8 | LA16 | Bit d'adresse 17 | |

| C9 | /MEMR | Memory Read (Active on all memory read cycles) | |

| C10 | /MEMW | Memory Write (Active on all memory write cycles) | |

| C11 | SD08 | Bit de donnée 8 | |

| C12 | SD09 | Bit de donnée 9 | |

| C13 | SD10 | Bit de donnée 10 | |

| C14 | SD11 | Bit de donnée 11 | |

| C15 | SD12 | Bit de donnée 12 | |

| C16 | SD13 | Bit de donnée 13 | |

| C17 | SD14 | Bit de donnée 14 | |

| C18 | SD15 | Bit de donnée 15 | |

| D1 | /MEMCS16 | Memory 16-bit chip select (1 wait, 16-bit memory cycle) | |

| D2 | /IOCS16 | I/O 16-bit chip select (1 wait, 16-bit I/O cycle) | |

| D3 | IRQ10 | Requête d'interruption 10 | |

| D4 | IRQ11 | Requête d'interruption 11 | |

| D5 | IRQ12 | Requête d'interruption 12 | |

| D6 | IRQ15 | Requête d'interruption 15 | |

| D7 | IRQ14 | Requête d'interruption 14 | |

| D8 | /DACK0 | Quittance DMA 0 | |

| D9 | DRQ0 | Requête DMA 0 | |

| D10 | /DACK5 | Quittance DMA 5 | |

| D11 | DRQ5 | Requête DMA 5 | |

| D12 | /DACK6 | Quittance DMA 6 | |

| D13 | DRQ6 | Requête DMA 6 | |

| D14 | /DACK7 | Quittance DMA 7 | |

| D15 | DRQ7 | Requête DMA 7 | |

| D16 | +5 V | ||

| D17 | /MASTER | Used with DRQ to gain control of system | |

| D18 | GND | Masse |

Articles connexes

- Portail de l’électricité et de l’électronique

- Portail de l’informatique