Cache de processeur

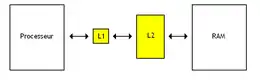

Un cache de processeur est une antémémoire matérielle utilisée par l'unité centrale de traitement (CPU) d'un ordinateur pour réduire le coût moyen (temps ou énergie) de l’accès aux données de la mémoire principale. Un cache de processeur est une mémoire plus petite et plus rapide, située au plus près d'une unité centrale de traitement (ou d'un cœur de microprocesseur), qui stocke des copies des données à partir d'emplacements de la mémoire principale qui sont fréquemment utilisés avant leurs transmissions aux registres du processeur. La plupart des CPU ont différents caches indépendants, y compris des caches d'instructions et de données, où le cache de données est généralement organisé comme une hiérarchie de plusieurs niveaux d'antémémoire (L1, L2, L3, L4, etc.). Les caches de processeur font partie de la mémoire centrale tout comme les registres de processeur et la mémoire principale, ils sont essentiels au fonctionnement de l'ordinateur.

Tous les processeurs (rapides) modernes, à quelques exceptions près, ont plusieurs niveaux de caches de processeur. Les premiers processeurs qui utilisaient un cache n'avaient qu'un seul niveau de cache ; contrairement aux caches de premier niveau ultérieurs, il n'était pas divisé en L1d (pour les données) et L1i (pour les instructions). Presque tous les CPU actuels avec des caches ont un cache L1 divisé. Ils ont également des caches L2 et pour les plus gros processeurs, des caches L3 également. Le cache L2 n'est généralement pas divisé et agit comme un référentiel commun pour le cache L1 déjà divisé. Chaque cœur d'un microprocesseur multi-cœur possède un cache L1 dédié et n'est généralement pas partagé entre les cœurs. Le cache L2 et les caches de niveau supérieur peuvent être partagés entre les cœurs[1]. Le cache L4 est actuellement rare et se trouve généralement sur une sorte de mémoire vive dynamique (DRAM), plutôt que sur une mémoire vive statique à accès aléatoire (SRAM), sur un dé de circuit intégré ou une puce électronique séparée (exceptionnellement, un cache de type eDRAM peut être utilisé pour tous les niveaux de cache, jusqu'à L1). Historiquement, c'était également le cas avec le cache L1, alors que des puces plus grandes ont permis son intégration et généralement à tous les niveaux de cache, à l'exception peut-être du dernier niveau. Chaque niveau de cache supplémentaire est optimisé différemment et a tendance à être plus grand que le précédent.

Il existe d'autres types de caches tels que le tampon de traduction (TLB) qui fait partie de l'unité de gestion mémoire (MMU) et qui équipe la plupart des CPU.

Notes et références

- (en) Cet article est partiellement ou en totalité issu de l’article de Wikipédia en anglais intitulé « CPU cache » (voir la liste des auteurs).

- Franck Delattre, « L'architecture Intel Nehalem », sur hardware.fr, HardWare.fr, (consulté le )