I²S

I²S (Inter-IC Sound, pronounced "eye-squared-ess"), is an electrical serial bus interface standard used for connecting digital audio devices together. It is used to communicate PCM audio data between integrated circuits in an electronic device. The I²S bus separates clock and serial data signals, resulting in simpler receivers than those required for asynchronous communications systems that need to recover the clock from the data stream. Alternatively I²S is spelled I2S (pronounced eye-two-ess) or IIS (pronounced eye-eye-ess). Despite the similar name, I²S is unrelated to the bidirectional I²C (IIC) bus.

| Type | Serial communication bus | ||

|---|---|---|---|

| Production history | |||

| Designer | Philips Semiconductor, known today as NXP Semiconductors | ||

| Designed | 1986 | ||

| Data | |||

| Data signal | Push-pull | ||

| Width |

1 data line (SD) + 2 clock lines (SCK, WS) | ||

| Protocol | Serial | ||

History

This standard was introduced in 1986 by Philips Semiconductor (now NXP Semiconductors) and was first revised June 5, 1996.[1] The standard was last revised on February 17, 2022 and updated terms master and slave to controller and target.[2]

Details

The I²S protocol outlines one specific type of PCM digital audio communication with defined parameters outlined in the Philips specification.

The bus consists of at least three lines:

- Bit clock line

- Word clock line

- At least one multiplexed data line

It may also include the following lines:

- Master clock (typically 256 x LRCLK)

- A multiplexed data line for upload

The bit clock pulses once for each discrete bit of data on the data lines. The bit clock frequency is the product of the sample rate, the number of bits per channel and the number of channels. So, for example, CD Audio with a sample frequency of 44.1 kHz, with 16 bits of precision and two channels (stereo) has a bit clock frequency of:

- 44.1 kHz × 16 × 2 = 1.4112 MHz

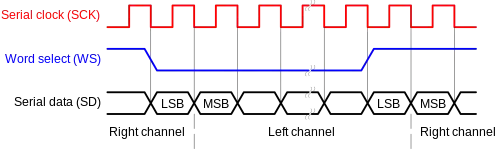

The word select clock lets the device know whether channel 0 or channel 1 is currently being sent, because I²S allows two channels to be sent on the same data line. It is a 50% duty-cycle signal that has the same frequency as the sample frequency. For stereo material, the I²S specification states that left audio is transmitted on the low cycle of the word select clock and the right channel is transmitted on the high cycle. It is typically synchronized to the falling edge of the serial clock, as the data is latched on the rising edge.[1] The word select clock changes one bit clock period before the MSB is transmitted. This enables, for example, the receiver to store the previous word and clear the input for the next.[1]

Data is signed, encoded as two's complement with the MSB (most significant bit) first.[1] This allows the number of bits per frame to be arbitrary, with no negotiation required between transmitter and receiver.[1]

As an audio interconnect

In audio equipment, I²S is sometimes used as an external link between a CD player or digital audio streaming device and an external digital-to-analog converter, as opposed to a purely internal connection within one player box. This may form an alternative to the commonly used AES/EBU, Toslink or S/PDIF standards.

The I²S connection was not intended to be used via cables, and most integrated circuits will not have the correct impedance for coaxial cables. As the impedance adaptation error associated with the different line lengths can cause differences in propagation delay between the clock line and data line, this can result in synchronization problems between the SCK, WS and data signals, mainly at high sampling frequencies and bitrates. As the I²S bus doesn't have any error detection mechanism, this can cause significant decoding errors.

There is no standard interconnecting cable for this application. Some manufacturers simply provide three BNC connectors, an 8P8C ("RJ45") socket or a DE-9 connector. Others like Audio Alchemy (now defunct) used DIN connectors. PS Audio, Musica Pristina and Wyred4Sound use an HDMI connector.[7] Dutch manufacturer Van Medevoort has implemented Q-link in some of its equipment, which transfers I²S over 4 RCA connectors (data, MCK, LRCK, BCK).

References

- "I²S Specification" (PDF). Philips Semiconductors. June 5, 1996. Archived from the original (PDF) on January 2, 2007.

- "UM11732 I2S bus specification" (PDF). NXP. Retrieved 19 March 2022.

- Lewis, Jerad (January 2012). "Technical Article MS-2275: Common Inter-IC Digital Interfaces for Audio Data Transfer" (PDF). Analog Devices, Inc.

- "MCLK in I2S audio protocol". electronics.stackexchange.com. Retrieved 2016-11-04.

Clock source for the delta-sigma modulators and digital filters. ... It is the clock that is used by the audio codec ... to time and/or drive its own internal operation.

- "PCM1781 (or any I2S DAC) clock sources - Audio Converters Forum - Audio Converters - TI E2E Community". e2e.ti.com. Retrieved 2016-11-04.

True, the master (modulator) clock is not part of the I2S standard

- Arbona, Jorge (September 2010). "Application Report SLAA469 Audio Serial Interface Configurations for Audio Codecs" (PDF).

Audio converters based on the delta-sigma (ΔΣ) architecture require an internal master clock that operates at a much faster rate than the target sample rate.

- McGowan, Paul (2010-04-02). "I2S standards from PS Audio". diyAudio. Retrieved 2022-09-11.

External links

- I²S Specification - Philips/NXP

- I²S and STM32F4 Slides - Auburn University

- Common inter-IC digital interfaces for audio data transfer, PDF