MOS Technology 8502

The MOS Technology 8502 is an 8-bit microprocessor designed by MOS Technology and used in the Commodore 128 (C128). It is an improved version of the MOS 6510 used in the Commodore 64 (C64). It was manufactured using the HMOS process, allowing it to have higher transistor density, and lower cost, while dissipating less heat. The 8502 allows the C128 to run at double the clock rate of the C64 with some limitations.

MOS 8502 | |

| General information | |

|---|---|

| Common manufacturer(s) | |

| Performance | |

| Max. CPU clock rate | 1.97 MHz to 2.046 MHz |

| Architecture and classification | |

| Instruction set | NMOS 6502/6510 |

| Physical specifications | |

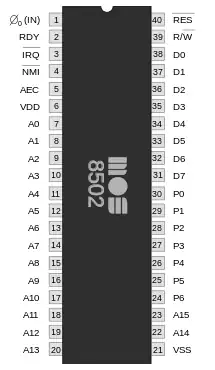

| Package(s) |

|

| History | |

| Predecessor(s) | MOS 6510 |

| Successor(s) | CSG 65CE02 |

Description

Memory access in 8-bit machines

Common random-access memory (RAM) of the Commodore C64-era allowed accesses at 2 MHz. If the CPU and display chip both shared the same memory to communicate, which was the common solution in the era when RAM was expensive, then one would normally have to have the CPU and display chip chips mediate access to the bus so that only one of them used it at a time, generally by having one pause the other. Assuming the two chips require roughly equal access, that means the chips are paused half of the time, effectively running at 1 MHz.[lower-alpha 1]

The 6502-family had a feature that eased the design of such systems. The 6502 used a two-phase clock to drive its internal circuitry, but only accessed memory during one of the two phases. That meant the display chip could access memory during alternating clock phases without having to pause the CPU. The major advantage of this style of access is that the two chips do not have to communicate to pause each other, they simply watch the already-existing clock signal present on the 6502's pins. In the original C64, this timing trick was used to allow the VIC-II to interleave its access to main memory with that of the 6510.[lower-alpha 2]

8502

The 8502 is mostly a conversion of the original 6502 to be fabricated on Intel's HMOS-II process, introduced in 1979 and available for 3rd party use. This process used smaller feature sizes, which allowed the same chip to be produced within a smaller area, and thus be lower cost. As a result of being smaller, the chip also required less energy to run and dissipated less heat. This made it useful in some roles where the original 6502 might not be appropriate.

The original 6502 came in three versions, A, B and C, differing in their maximum speed, 1, 2 or 4 MHz, respectively. There was no physical difference between these designs; if a particular chip ran successfully at 2 MHz in testing it was labeled B, otherwise A. With the move to the HMOS process, most of the 8502s were capable of running at 2 MHz, the equivalent of the 6502B.

Changing the running speed of a 6502-based processor is as simple as changing the input clock signal, which meant the 8502 could easily switch between 2 MHz and the 6510's 1 MHz. When the clock runs at double-speed, it faces the problem that there is not enough time for the VIC to access memory during the free half-cycles. For this reason, the 8502 could only run at double-speed full-time when being used with the 80-column VDC in the C128, which had separate memory for the display that was not being directly accessed by the CPU.

When running a VIC display mode, the two chips began to share access as was the case in the C64, and this meant the CPU had to return to its normal ~1 MHz speed. Programs could disable the screen during CPU-intensive calculations to allow the CPU to run at its faster speed. A smaller speed gain, about 35%, was also possible while keeping the VIC display active by switching the CPU to 2 MHz only while the VIC is drawing the empty border along the top and bottom of the screen, since the VIC performs no RAM access during that time.

The pinout is slightly different than the 6510. The 8502 has an extra I/O-pin (the built-in I/O port mapped to addresses 0 and 1 is extended from 6 to 7 bits) and lacks the ϕ2-pin that the 6510 had. The 8502 family also includes the MOS 7501, 8500 and 8501.

Notes

- In practice, due to the exact timing of television signals, the CPU does have more time available on the bus than the display chip.

- Most 6502-based machines of the era used this concept, which is why the 1 MHz speed of the CPU is common on machines with 2 MHz RAM - The PET ran at 1 MHz, the Apple II at 1.02, etc. For comparison, the Atari 8-bit family used the explicit pausing solution, which offered higher performance but needed additional circuitry, and later, a custom version of the CPU. The BBC Micro used interleaving like the C64, but had 4 MHz RAM, allowing it to run the CPU and display at 2 MHz.

References

- Service Manual C-128/C128D Computer. Commodore Business Machines. November 1987. PN-314001-08