NEC V60

The NEC V60[1][2] is a CISC microprocessor manufactured by NEC starting in 1986. Several improved versions were introduced with the same instruction set architecture (ISA), the V70 in 1987, and the V80 and AFPP in 1989. They were succeeded[3] by the V800 product families, which is currently produced by Renesas Electronics.

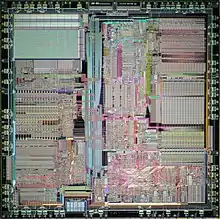

Die shot of NEC V60 microprocessor Name "V60 D70616" in bottom center | |

| General information | |

|---|---|

| Launched | V60: 1986 V70: 1987 V80: 1989 AFPP: 1989 |

| Common manufacturer(s) | |

| Performance | |

| Max. CPU clock rate | V60: 16 MHz V70: 20/25 MHz V80: 25/33 MHz AFPP: 20 MHz |

| Data width | V60: 16 (int. 32) V70: 32 V80: 32 |

| Address width | V60: 24 (int. 32) V70: 32 V80: 32 |

| Virtual address width | 32 Linear[1] |

| Cache | |

| L1 cache | V80: 1K/1K |

| Architecture and classification | |

| Application | Embedded systems, minicomputers, arcade games |

| Technology node | V60: 1.5/1.2 μm V70: 1.5/1.2 μm V80: 0.8 μm AFPP: 1.2 μm |

| Microarchitecture | "V60/V70", "V80" |

| Instruction set | NEC V60-V80[1] |

| Extensions |

|

| Number of instructions | V60/V70: 119 V80: 123 |

| Physical specifications | |

| Transistors |

|

| Co-processor | AFPP (μPD72691) |

| Package(s) | |

| Products, models, variants | |

| Product code name(s) |

|

| History | |

| Predecessor(s) | V20-V50 |

| Successor(s) | V800 Series |

The V60 family includes a floating-point unit[4] (FPU) and memory management unit (MMU) and real-time operating system (RTOS) support for both Unix-based user-application-oriented systems[5] and I-TRON–based hardware-control-oriented embedded systems. They can be used in a multi-cpu lockstep fault-tolerant mechanism named FRM. Development tools included Ada certified system MV-4000, and an in-circuit emulator (ICE).

The V60/V70/V80's applications covered a wide area, including circuit switching telephone exchanges, minicomputers, aerospace guidance systems,[6] word processors, industrial computers, and various arcade games.

Introduction

NEC V60[2][1] is a CISC[7] processor manufactured by NEC starting in 1986.[8] It was the first 32-bit general-purpose microprocessor commercially available in Japan.[9]

Based on a relatively traditional design for the period,[10][11][12][13][14] the V60 was a radical departure from NEC's previous, 16-bit V–series processor, the V20-V50,[15] which were based on the Intel 8086 model,[7] although the V60 had the ability to emulate the V20/V30.[1]: §10

According to NEC's documentation, this computer architectural change was due to the increasing demands for, and the diversity of, high-level programming languages. Such trends called for a processor with both improved performance, achieved by doubling the bus width to 32 bits, and with greater flexibility facilitated by having a large number of general-purpose registers.[2][1] These were common features of RISC chips.[16] At the time, a transition from CISC to RISC seemed to bring many benefits for emerging markets.

Today, RISC chips are common, and CISC designs—such as Intel's x86 and the 80486—which have been mainstream for several decades, internally adopt RISC features in their microarchitectures.[17][18] According to Pat Gelsinger, binary backward compatibility for legacy software is more important than changing the ISA.[19]

Overview

Instruction set

The V60 (a.k.a. μPD70616) retained a CISC architecture.[20] Its manual describes their architecture as having "features of high-end mainframe and supercomputers", with a fully orthogonal instruction set that includes non-uniform-length instructions, memory-to-memory operations that include string manipulation, and complex operand-addressing schemes.[1][2][16]

Family

The V60 operates as a 32-bit processor internally, while externally providing 16-bit data, and 24-bit address, buses. In addition, the V60 has 32 32-bit general-purpose registers.[1]: §1 Its basic architecture is used in several variants. The V70 (μPD70632), released in 1987, provides 32-bit external buses. Launched in 1989, the V80 (μPD70832)[21] is the culmination of the series: having on-chip caches, a branch predictor, and less reliance on microcode for complex operations.[22]

Software

The operating systems developed for the V60-V80 series are generally oriented toward real-time operations. Several OSs were ported to the series, including real-time versions of Unix and I-TRON.[23][24]

Because the V60/V70 was used in various Japanese arcade games, their instruction set architecture is emulated in the MAME CPU simulator.[25] The latest open-source code is available from the GitHub repository.[26]

FRM

All three processors have the FRM (Functional Redundancy Monitoring) synchronous multiple modular lockstep mechanism, which enables fault-tolerant computer systems. It requires multiple devices of the same model, one of which then operates in "master mode", while the other devices listen to the master device, in "checker mode". If two or more devices simultaneously output different results via their "fault output" pins, a majority-voting decision can be taken by external circuits. In addition, a recovery method for the mismatched instruction—either "roll-back by retry" or "roll-forward by exception"—can be selected via an external pin.[27][28][1]: §11 [21][29][30]: §3–229, 266

| Pin Name | I/O | Function |

|---|---|---|

| BMODE (FRM) | Input | Select the normal bus (master) mode or FRM operating (checker) mode |

| BLOCK (MSMAT) | Output | Master output requesting bus lock, i.e. freezing bus operation Checker output indicating a mismatch has been detected |

| BFREZ | Input | Assertion for freezing bus operation |

| RT/EP | Input | Selecting input for "roll-back by retry" or "roll-forward by exception" |

V60

The work on V60 processor began in 1982 with about 250 engineers under the leadership of Yoichi Yano,[31] and the processor debuted in February 1986.[32] It had a six-stage pipeline, built-in memory-management unit, and floating-point arithmetic. It was manufactured using a two-layer aluminum metal CMOS process technology, under a 1.5 μm design rule, to implement 375,000 transistors on a 13.9 × 13.8 mm2 die.[8][33] It operates at 5 V and was initially packaged in a 68-pin PGA.[34] The first version ran at 16 MHz and attained 3.5 MIPS.[33] Its sample price at launch was set at ¥100,000 ($588.23). It entered full-scale production in August 1986.[33]

Sega employed this processor for most of its arcade game sets in the 1990s; both the Sega System 32 and the Sega Model 1 architectures used V60 as their main CPU. (The latter used the lower-cost μPD70615 variant,[35] which doesn't implement V20/V30 emulation and FRM.[36]) The V60 was also used as the main CPU in the SSV arcade architecture—so named because it was developed jointly by Seta, Sammy, and Visco.[37] Sega originally considered using a 16 MHz V60 as the basis for its Sega Saturn console; but after receiving word that the PlayStation employed a 33.8 MHz MIPS R3000A processor, instead chose the dual-SH-2 design for the production model.[38]

In 1988, NEC released a kit called PS98-145-HMW[39] for Unix enthusiasts. The kit contained a V60 processor board that could be plugged into selected models of the PC-9800 computer series and a distribution of their UNIX System V port, the PC-UX/V Rel 2.0 (V60), on 15 8-inch floppy disks. The suggested retail price for this kit was 450,000 Yen.[39] NEC-group companies themselves intensively employed the V60 processor. Their telephone circuit switcher (exchange), which was one of the first intended targets, used V60. In 1991, they expanded their word processor products line with Bungou Mini (文豪ミニ in Japanese) series 5SX, 7SX, and 7SD, which used the V60 for fast outline font processing, while the main system processor was a 16 MHz NEC V33.[40][41] In addition, V60 microcode variants were employed in NEC's MS-4100 minicomputer series, which was the fastest one in Japan at that time.[42][43][44]

V70

The V70 (μPD70632) improved on the V60 by increasing the external buses to 32 bits, equal to the internal buses. It was also manufactured in 1.5 μm with a two-metal layer process. Its 14.35 × 14.24 mm2 die had 385,000 transistors and was packaged in a 132-pin ceramic PGA. Its MMU had support for demand paging. Its floating-point unit was IEEE 754 compliant.[29] The 20 MHz version attained a peak performance of 6.6 MIPS and was priced, at launch in August 1987, at ¥100,000 ($719.42). The initial production capacity was 20,000 units per month.[45] A later report describes it as fabricated in 1.2-micrometer CMOS on a 12.23 × 12.32 mm2 die.[21] The V70 had a two-cycle non-pipeline (T1-T2) external bus system, whereas that of the V60 operated at 3 or 4 cycles (T1-T3/T4).[21][2] Of course, the internal units were pipelined.

The V70 was used by Sega in its System Multi 32[46] and by Jaleco in its Mega System 32. (See the photo of the V70 mounted on the latter system's printed circuit board.)[47]

JAXA embedded its variant of the V70, with the I-TRON RX616 operating system, in the Guidance Control Computer of the H-IIA carrier rockets, in satellites such as the Akatsuki (Venus Climate Orbiter), and the Kibo International Space Station (ISS) module.[6][48][49] The H-IIA launch vehicles were deployed domestically, in Japan, although their payloads included satellites from foreign countries. As described in JAXA's LSI (MPU/ASIC) roadmap, this V70 variant is designated "32bit MPU (H32/V70)", whose development, probably including the testing (QT) phase, was "from the middle of 1980s to early 1990s".[50]: 9 [51] This variant was used until its replacement, in 2013, by the HR5000 64-bit, 25 MHz microprocessor, which is based on the MIPS64-5Kf architecture,[52] fabricated by HIREC, whose development was completed around 2011.[53][54][55]

"Space Environment Data Acquisition" for the V70 was done at the Kibo-ISS exposed facility.

| Item | Part No. | SEE (Single Event Effect) Monitored Item |

Result[56] |

|---|---|---|---|

| V70-MPU | NASDA 38510/92101xz | SEU (Single Event Upset) SEL (Single Event Latch-up) | Not observed (—2010/9/30) |

V80

The V80 (μPD70832)[21] was launched in the spring of 1989. By incorporating on-chip caches and a branch predictor, it was declared NEC's 486 by Computer Business Review.[57][58] The performance of the V80 was two to four times than that of the V70, depending on application. For example, compared with V70, the V80 had a 32-bit hardware multiplier that reduced the number of cycles required to complete an integer-multiplication machine-instruction from 23 to 9. (For more detailed differences, see the hardware architecture section below.) The V80 was manufactured in a 0.8-micrometer CMOS process on a die area of 14.49 × 15.47 mm2, implementing 980,000 transistors. It was packaged in a 280-pin PGA, and operated at 25 and 33 MHz with claimed peak performances of 12.5 and 16.5 MIPS, respectively. The V80 had separate 1 KB on-die caches for both instructions and data. It had a 64-entry branch predictor, a 5% performance gain being attributed to it. The launch prices of the V80 were cited as equivalent to $1200 for the 33 MHz model and $960 for the 25 MHz model. Supposedly, a 45 MHz model was scheduled for 1990,[58] but it did not materialize.

The V80, with μPD72691 co-FPP and μPD71101 simple peripheral chips, was used for an industrial computer running the RX-UX832 real-time UNIX operating system and a X11-R4-based windowing system.[59][60]

AFPP (co-FPP)

The Advanced Floating Point Processor (AFPP) (μPD72691) is a co-processor for floating-point arithmetic operations.[61] The V60/V70/V80 themselves can perform floating-point arithmetic, but they are very slow because they lack hardware dedicated to such operations. In 1989, to compensate V60/V70/V80 for their fairly weak floating-point performance, NEC launched this 80-bit floating-point co-processor for 32-bit single precision, 64-bit double precision, and 80-bit extended precision operations according to IEEE 754 specifications.[4][21] This chip had a performance of 6.7 MFLOPS, doing vector-matrix multiplication while operating at 20 MHz. It was fabricated using a 1.2-micrometer double-metal layer CMOS process, resulting in 433,000 transistors on an 11.6 × 14.9 mm2 die.[4] It was packaged in a 68-pin PGA. This co-processor connected to a V80 via a dedicated bus, to a V60 or V70 via a shared main bus, which constrained peak performance.[21]

Hardware architecture

The V60/V70/V80 shared a basic architecture. They had thirty-two 32-bit general-purpose registers, with the last three of them commonly used as stack pointer, frame pointer, and argument pointer, which well matched high level language compilers' calling conventions.[29][62] The V60 and V70 have 119 machine instructions,[29] with that number being extended slightly to 123 instructions for the V80. The instructions are of non-uniform length, between one and 22 bytes,[1] and take two operands, both of which can be addresses in main memory.[21] After studying the V60's reference manual, Paul Vixie described it as "a very VAX-ish arch, with a V20/V30 emulation mode (which[...] means it can run Intel 8086/8088 software)".[63]

The V60–V80 has a built-in memory management unit (MMU)[8][61] that divides a 4-GB virtual address space into four 1-GB sections, each section being further divided into 1,024 1-MB areas, and each area being composed of 256 4-KB pages. On the V60/V70, four registers (ATBR0 to ATBR3) store section pointers, but the "area tables entries" (ATE) and page tables entries (PTE) are stored in off-chip RAM. The V80 merged the ATE and ATBR registers—which are both on-chip, with only the PTE entries stored in external RAM—allowing for faster execution of translation lookaside buffer (TLB) misses by eliminating one memory read.[21]

The translation lookaside buffers on the V60/70 are 16-entry fully associative with replacement done by microcode. The V80, in contrast, has a 64-entry 2-way set associative TLB with replacement done in hardware. TLB replacement took 58 cycles in the V70 and disrupted the pipelined execution of other instructions. On the V80, a TLB replacement takes only 6 or 11 cycles depending on whether the page is in the same area; pipeline disruption no longer occurs in the V80 because of the separate TLB replacement hardware unit, which operates in parallel with the rest of the processor.[21]

All three processors use the same protection mechanism, with 4 protection levels set via a program status word, Ring 0 being the privileged level that could access a special set of registers on the processors.[21]

All three models support a triple-mode redundancy configuration with three CPUs used in a byzantine fault–tolerance scheme with bus freeze, instruction retry, and chip replacement signals.[21][28] The V80 added parity signals to its data and address buses.[21]

String operations were implemented in microcode in the V60/V70; but these were aided by a hardware data control unit, running at full bus speed, in the V80. This made string operations about five times faster in the V80 than in the V60/V70.[21]

All floating-point operations are largely implemented in microcode across the processor family and are thus fairly slow. On the V60/V70, the 32-bit floating-point operations take 120/116/137 cycles for addition/multiplication/division, while the corresponding 64-bit floating-point operations take 178/270/590 cycles. The V80 has some limited hardware assist for phases of floating-point operations—e.g. decomposition into sign, exponent, and mantissa—thus its floating-point unit was claimed to be up to three times as effective as that of the V70, with 32-bit floating-point operations taking 36/44/74 cycles and 64-bit operations taking 75/110/533 cycles (addition/multiplication/division).[21]

Operating systems

Unix (non-real-time and real-time)

NEC ported several variants of the Unix operating system to its V60/V70/V80 processors for user-application-oriented systems, including real-time ones. The first flavor of NEC's UNIX System V port for V60 was called PC-UX/V Rel 2.0 (V60).[64] (Also refer to external link photos below.) NEC developed a Unix variant with a focus on real-time operation to run on V60/V70/V80. Called Real-time UNIX RX-UX 832, it has a double-layered kernel structure, with all task scheduling handled by the real-time kernel.[5] A multiprocessor version of RX-UX 832 was also developed, named MUSTARD (Multiprocessor Unix for Embedded Real-Time Systems).[65] The MUSTARD-powered computer prototype uses eight V70 processors. It utilizes FRM function, and can configure and change the configuration of master and checker upon request.[66][67]

I-TRON (real-time)

For hardware-control-oriented embedded systems, the I-TRON-based real-time operating system, named RX616, was implemented by NEC for the V60/V70.[27][23] The 32-bit RX616 was a continuous fork from the 16-bit RX116, which was for the V20-V50.[45][24]

FlexOS (real-time)

In 1987, Digital Research, Inc. also announced that they were planning on porting FlexOS to the V60 and V70.[68]

CP/M and DOS (legacy 16-bit)

The V60 could also run CP/M and DOS programs (ported from the V20-V50 series) using V20/V30 emulation mode.[33] According to a 1991 article in InfoWorld, Digital Research was working on a version of Concurrent DOS for the V60 at some point; but this was never released, as the V60/V70 processors were not imported to the US for use in PC clones.[69]

Development tools

C/C++ cross-compilers

As part of its development tool kit and integrated development environment (IDE), NEC had its own C-compiler, the PKG70616 "Software Generation tool package for V60/V70".[70] In addition, GHS (Green Hills Software) made its native mode C compiler (MULTI), and MetaWare, Inc. (currently Synopsys, via ARC International) made one, for V20/V30 (Intel 8086), emulation mode, called High C/C++.[71][18]: acknowledgement Cygnus Solutions (currently Red Hat) also ported GCC as a part of an enhanced GNU compiler system (EGCS) fork,[72] but it seems not to be public.[73][74]

As of 2018, the processor-specific directory necv70 is still kept alive in the newlib C-language libraries (libc.a and libm.a) by RedHat.[75] Recent maintenance seems to be done on Sourceware.org. The latest source code is available from its git repository.[76]

MV-4100 Ada 83–certified system

The Ada 83–certified "platform system" was named MV-4000, certified as "MV4000". This certification was done with a target system, that utilized the real-time UNIX RX-UX 832 OS running on a VMEbus (IEEE 1014)–based system with a V70 processor board plugged in. The host of the cross compiler was an NEC Engineering Work Station EWS 4800, whose host OS, EWS-US/V, was also UNIX System V–based.[77][78][79][80]

The processor received Ada-83 validation from AETECH, Inc.,[77] running the Ada Compiler Validation Capability tests.[81]

| System Name | Certificate Number | Compiler Type | HOST Machine | HOST OS | TARGET Machine | TARGET OS |

|---|---|---|---|---|---|---|

| NEC Ada Compiler System for EWS-UX/V to V70/RX-UX832, Version 1.0 | 910918S1.11217 | Base | NEC EWS4800/60 | EWS-UX/V R8.1 | NEC MV4000 | RX-UX832 V1.6 |

| NEC Ada Compiler System for EWS-UX/V(Release 4.0) to V70/RX-UX832 Version Release 4.1 (4.6.4) | 910918S1.11217 | Derived | EWS4800 Superstation RISC Series | EWS-UX/V(R4.0) R6.2 | NEC MV4000 | RX-UX832 V1.63 |

| MV-4000 Features[78] |

|---|

| System bus: IEEE1014 D1.2/IEC821 Rev C.1 (8-slot) |

| Expansion bus: IEC822 Rev C or V70 cache bus (6-slot) |

| Built-in 100M byte (formatted) 3.5-inch SCSI hard disk |

| Built-in 1M-byte 3.5-inch floppy disk drive 1 |

| Expansion SCSI (1 ch) |

| EMI evaluation: VCCI - 1 kind |

Evaluation board kits

NEC released some plug-in evaluation board kits for the V60/V70.

| Parts No. | Descriptions | Remarks |

|---|---|---|

| EBIBM-7061UNX | V60 coprocessor slave board with Unix for PC-XT/AT | w/ PC-UX/V Rel 2.0 (V60) |

| PS98-145-HMW | V60 coprocessor slave board with Unix for NEC PC-9801 | w/ PC-UX/V Rel 2.0 (V60) |

| EBIBM-70616SBC | V60 single board computer for Multibus I | |

| A part of MV-4000 | V70 single board computer for VMEbus | Ada 83 certified |

In-circuit emulator

On-chip software debug support with the IE-V60

NEC based its own full (non-ROM and non-JTAG) probe-based in-circuit emulator, the IE-V60, on the V60, because V60/V70 chips themselves had emulator-chip capabilities. The IE-V60 was the first in-circuit emulator for V60 that was manufactured by NEC. It also had a PROM programmer function.Section 9.4, p. 205[2] NEC described it as a "user friendly software debug function". The chips have various trapping exceptions, such as data read (or write) to the user specified address, and 2 break-points simultaneously.Section 9[1]

External bus status pins

The external bus system indicates its bus status using 3 status pins, which provide three bits to signal such conditions as first instruction fetch after branch, continuous instruction fetch, TLB data access, single data access, and sequential data access. Section 6.1, p. 114 [2]

| ST[2:0] | Description |

|---|---|

| 111 | Instruction fetch |

| 011 | Instruction fetch after branch |

| 101 | "TLB" data access |

| 100 | "System base (interrupt & exception vector) table" data access |

| 011 | Single data access |

| 010 | Short-path data access (Skipped address by read-after-write) |

| 001 | Sequential data access |

Debugging with V80

These software and hardware debugging functions were also built into the V80. However, the V80 did not have an in-circuit emulator, possibly because the presence of such software as real-time UNIX RX-UX 832 and real-time I-TRON RX616 rendered such a function unnecessary. Once Unix boots up, there is no need for an in-circuit emulator for developing either device drivers or application software. What is needed is a C compiler, a cross compiler, and a screen debugger—such as GDB-Tk—that works with the target device,.

HP 64758

Hewlett-Packard (currently Keysight) offered probing-pod-based in-circuit emulation hardware for the V70, built on their HP 64700 Series systems,[82][83] the successor to the HP 64000 Series, specifically the HP 64758.[84][85][82] It enables trace function like a logic analyzer. This test equipment also displays disassembled source code automatically, with trace data display and without an object file,[82] and displays high-level language source code when the source code and the object files are provided and they were compiled in DWARF format. An interface for the V60 (10339G) was also in the catalog,[85] but the long probing-pod cable required "special grade qualified" devices, i.e. the high-speed grade V70.

HP 64758: Main units, sub-units, and hosted interface

| Product | Description |

|---|---|

| 64758A | V70 20 MHz Emulator with 512KB of emulation memory |

| 64758AX | One-Time-Update |

| 64758B | V70 20MHZ Emulator with 1MB of emulation memory |

| 64758G | V70 20 MHz Emulation Subsystem, 512KB |

| 64758H | V70 20 MHz Emulation Subsystem, 1MB |

| 64758S | V70 (uPD70632)–hosted User Interface |

Software options

| Product | Description |

|---|---|

| 64879L | V70 Assembler/Linker, Single-user License |

| 64879M | V70 Assembler/Linker, Media & Manuals |

| 64879U | V70 Assembler/Linker Multi-user license |

Hardware options

| Product | Description |

|---|---|

| B3068B | V70-Hosted Graphical User Interface |

| 10339G | NEC V60 Interface |

| E2407A | NEC V70 Interface |

Failings

Strategic failure of the V80 microarchitecture

In its development phase, the V80 was thought to have the same performance as the Intel 80486,[86] but they ended up having many different features. The internal execution for each instruction of the V80 needed at least two cycles, while that of i486 required one. The internal pipeline of the V80 seemed buffered asynchronous, but that of i486 was synchronous. In other words, the internal microarchitecture of V80 was CISC, but that of i486 was RISC. Both of their ISAs allowed long non-uniform CISC instructions, but the i486 had a wider, 128-bit internal cache memory bus, while that of V80 had a 32-bit width. This difference can be seen on their die photos.[21][18][22][17] The design was fatal from the performance point of view, but NEC did not change it. NEC might have been able to redesign the physical design, with the same register-transfer level, but it did not.

Lack of commercial success

The V60-V80 architecture did not enjoy much commercial success.[32]

The V60, V70, and V80 were listed in the 1989 and 1990 NEC catalogs in their PGA packaging.[87][88] A NEC catalog from 1995 still listed the V60 and V70 (not only in their PGA version but also in a QFP packaging, and also included a low-cost variant of the V60 named μPD70615, which eliminated V20/V30 emulation and FRM function), alongside their assorted chipsets; but the V80 was not offered in this catalog.[36] The 1999 edition of the same catalog no longer had any V60-V80 products.[89]

Successors

The V800 series

In 1992, NEC launched a new model, the V800 Series 32-bit microcontroller; but it did not have a memory management unit (MMU).[90] It had a RISC-based architecture, inspired by the Intel i960 and MIPS architectures, and other RISC processor instructions, such as JARL (Jump and Register Link) and load–store architecture.

At this time, the enormous software assets of the V60/V70, such as real-time Unix, were abandoned and never returned to their successors, a scenario Intel avoided.

The V800 Series had 3 major variants, the V810, V830, and V850 families.[91][3][92]

The V820 (μPD70742) was a simple variant of the V810 (μPD70732), but with peripherals.

The designation V840 may have been skipped as a designation because of Japanese tetraphobia (see page 58[36]). One Japanese pronunciation of "4" means "death", thus avoid names evoking such as Death-watch Shi-ban (the number 4 – Shi-ban) Bug (死番虫, precisely "deathwatch beetle").

As of 2005, it was already the V850 era, and the V850 family has been enjoying great success.[93] As of 2018, it is called the Renesas V850 family and the RH850 family, with V850/V850E1/V850E2 and V850E2/V850E3 CPU cores, respectively. Those CPU cores have extended the ISA of the original V810 core;[94] running with the V850 compiler.[95]

Modern software-based simulation

MAME

Because the V60/V70 had been used for many Japanese arcade games, MAME (for "Multiple Arcade Machine Emulator"), which emulates multiple old arcade games for enthusiasts, includes an CPU simulator for their instruction set architecture.[25] It is a kind of an instruction set simulator, not for developers but for users.

It has been maintained by the MAME development team. The latest open-source code, written in C++, is available from the GitHub repository.[96] The operation codes in the file optable.hxx are exactly the same as those of the V60.[1]

References

-

NEC (November 1986). μPD70616 Programmer's Reference Manual (PRELIMINARY ed.). The Internet Archive, a 501(c)(3) non-profit.

EPUB, KINDLE, PDF, PDF w/text, FULL TEXT, etc, are available -

Kani, Dr. Kenji (April 1987). Vシリーズマイクロコンピュータ 2 [V-Series Microcomputer 2] (in Japanese). Maruzen. ISBN 978-4621031575.

本書は日本電気(株)が、わが国ではじめて開発した32ビットマイクロプロセッサV60について解説したものである。[This book explains the V60, Japanese first developed 32-bit microprocessor by NEC.] -

Suzuki, Hiroaki; Sakai, Toshichika; Harigai, Hisao; Yano, Yoichi (1995-04-25). "A 0.9-V, 2.5 MHz CMOS 32-bit Microprocessor". IEICE Transactions on Electronics. E78-C (4): 389–393. ISSN 0916-8516. Retrieved 2018-01-09.

Summary:

A 32-bit RISC microprocessor "V810" that has 5-stage pipeline structure and a 1 Kbyte, direct-mapped instruction cache realizes 2.5 MHz operation at 0.9 V with 2.0 mW power consumption. The supply voltage can be reduced to 0.75 V. To overcome narrow noise margin, all the signals are set to have rail-to-rail swing by pseudo-static circuit technique. The chip is fabricated by a 0.8 μm double metal-layer CMOS process technology to integrate 240,000 transistors on a 7.4 mm7.1 mm die. -

Nakayama, T.; Harigai, H.; Kojima, S.; Kaneko, H.; Igarashi, H.; Toba, T.; Yamagami, Y.; Yano, Y. (Oct 1989). "A 6.7-MFLOPS floating-point coprocessor with vector/matrix instructions". IEEE Journal of Solid-State Circuits. 24 (5): 1324–1330. Bibcode:1989IJSSC..24.1324N. doi:10.1109/JSSC.1989.572608. ISSN 1558-173X.

Abstract:

An 80-bit floating-point coprocessor which implements 24 vector/matrix instructions and 22 mathematical functions is described. This processor can execute floating-point addition/rounding and pipelined multiplication concurrently, under the control of horizontal-type microinstructions. The SRT division method and CORDIC trigonometrical algorithm are used for a favorable cost/performance implementation. The performance of 6.7 MFLOPS in the vector-matrix multiplication at 20 MHz has been attained by the use of parallel operations. The vector/matrix instruction is about three times faster than conventional add and multiply instructions. The chip has been fabricated in 1.2- mu m double-metal layer CMOS process containing 433000 transistors on an 11.6*14.9-mm/sup 2/ die size. -

Mizuhashi, Yukiko; Teramoto, Msanoro (August 1989). "Real-time UNIX operating system: RX-UX 832". Microprocessing and Microprogramming. 27 (1–5): 533–538. doi:10.1016/0165-6074(89)90105-1.

Abstract:

This paper describes requirements for real-time UNIX operating systems, design concept and the implementation of RX-UX 832 real-time UNIX operating system for v60/v70 microprocessor which are NEC's 32-bit microprocessors. RX-UX 832 is implemented adopting the building block structure, composed of three modules, real-time kernel, file-server and Unix supervisor. To guarantee a real-time responsibility, several enhancements were introduced such as, fixed priority task scheduling scheme, contiguous block file system and fault tolerant functions.

Thus, RX-UX 832 allows system designers to use standard Unix as its man-machine interface to build fault tolerant systems with sophisticated operability and provides high-quality software applications on the high performance microchips. - "Akatsuki: Dawn rises again at Venus". 11 December 2015. Retrieved 2018-01-07.

-

Hardenbergh, Hal W (1988). "RISCs CISCs and Fabs". Programmer's Journal. Avant-Garde Creations. 6 (2): 15.

Google Books

So far we haven't mentioned two 32-bit CISC chips, the NEC V60/70 and the AT&T WE32 family. Unlike the NEC V20/25/30/50, the V60/70 is not based on the Intel architecture. NEC is targeting the V60/70 at embedded applications, ... -

Yamahata, Hitoshi; Suzuki, Nariko; Koumoto, Yasuhiko; Shiiba, Tadaaki (1987-02-06). "マイクロプロセッサV60のアーキテクチャ" [Architecture of the microprocessor V60] (PDF). SIG Technical Reports; Microcomputer 43-2 (in Japanese). Information Processing Society of Japan. 1987 (8(1986-ARC-043)): 1–8. AN10096105.

This report will describe a single chip 32-bit CMOS VLSI microprocessor V60. It has been implemented by using a double metal-layer CMOS process technology with 1.5 um design rule to integrate 375,000 transistors. It integrates the virtual memory management unit for demand paging and the floating-point operations that conform to the IEEE-754 Floating-Point Standard. By using V20/V30 emulation mode, it can directly execute object programs of 16-bit CPU (V30). Instruction formats are suited to code-generation phase of compilers. 237 instructions are provided for high-level language and operating system. It can execute 3.5 MIPS (Million Instructions per Second) at 16-MHz operation with 16-bit data bus. -

Sakamura, Ken (April 1988). "Recent Trends" (PDF). IEEE Micro. 8 (2): 10–11. ISSN 0272-1732. Retrieved 2018-01-08.

The V60/V70, NEC's proprietary CPU, is the first commercial-base, general-purpose, 32-bit microprocessor in Japan. -

Rowen, C.; Przbylski, S.; Jouppi, N.; Gross, T.; Shott, J.; Hennessy, J. (1984). "A pipelined 32b NMOS microprocessor". 1984 IEEE International Solid-State Circuits Conference. Digest of Technical Papers. Vol. XXVII. pp. 180–181. doi:10.1109/ISSCC.1984.1156607. S2CID 42147153.

Stanford MIPS -

Sherburne, R. W.; Katevenis, M. G. H.; Patterson, D. A.; Sequin, C. H. (1984). "A 32-bit NMOS microprocessor with a large register file". IEEE Journal of Solid-State Circuits. 19 (5): 682–689. Bibcode:1984IJSSC..19..682S. doi:10.1109/JSSC.1984.1052208. ISSN 0018-9200. S2CID 23195124.

UCB RISC-II -

Riordan, T.; Grewal, G. P.; Hsu, S.; Kinsel, J.; Libby, J.; March, R.; Mills, M.; Ries, P.; Scofield, R. (1988). "The MIPS M2000 system". Proceedings 1988 IEEE International Conference on Computer Design: VLSI. pp. 366–369. doi:10.1109/ICCD.1988.25724. ISBN 0-8186-0872-2. S2CID 60801545.

MIPS M2000 (R2000) -

Namjoo, M.; Agrawal, A.; Jackson, D. C.; Quach, L. (1988). "CMOS gate array implementation of the SPARC architecture". Digest of Papers. COMPCON Spring 88 Thirty-Third IEEE Computer Society International Conference. pp. 10–13. doi:10.1109/CMPCON.1988.4818. ISBN 0-8186-0828-5. S2CID 21078114.

SPARC, 1st Gen. -

Kohn, L.; Fu, S. W. (1989). "A 1,000,000 transistor microprocessor". IEEE International Solid-State Circuits Conference, 1989 ISSCC. Digest of Technical Papers. pp. 54–55. doi:10.1109/ISSCC.1989.48231. S2CID 58413700.

Intel 860 -

NEC (June 1997). 16-BIT V SERIES; INSTRUCTIONS (5 ed.). The Internet Archive, a 501(c)(3) non-profit.

EPUB, KINDLE, PDF, FULL TEXT, etc, are available. -

Hennessy: Stanford University, John L; Patterson: University of California at Berkeley, David A. (2007). Computer Architecture: A Quantitative Approach (Fourth ed.). Morgan Kaufmann Publishers. ISBN 978-0-12-370490-0.

Open Access: EPUB, KINDLE, PDF, FULL TEXT, etc, are available. -

Fu, B.; Saini, A.; Gelsinger, P. P. (1989). "Performance and microarchitecture of the i486 processor". Proceedings 1989 IEEE International Conference on Computer Design: VLSI in Computers and Processors. pp. 182–187. doi:10.1109/ICCD.1989.63352. ISBN 0-8186-1971-6. S2CID 62082864.

Intel 80486

Abstract:

The i486 microprocessor includes a carefully tuned, five-stage pipeline with an integrated 8-kB cache. A variety of techniques previously associated only with RISC (reduced-instruction-set computer) processors are used to execute the average instruction in 1.8 clocks. This represents a 2.5* reduction from its predecessor, the 386 microprocessor. The pipeline and clock count comparisons are described in detail. In addition, an onchip floating-point unit is included which yields a 4* clock count reduction from the 387 numeric coprocessor. The microarchitecture enhancements and optimizations used to achieve this goal, most of which are non-silicon-intensive, are discussed. All instructions of the 386 microprocessor and the 387 numeric coprocessor are implemented in a completely compatible fashion. - Crawford, J.H. (February 1990). "The i486 CPU: executing instructions in one clock cycle". IEEE Micro. 10 (1): 27–36. CiteSeerX 10.1.1.126.4216. doi:10.1109/40.46766. ISSN 0272-1732.

- "Despite its aging design, the x86 is still in charge". CNET.

-

Wade, James (1 October 1996). "A Community-Level Analysis of Sources and Rates of Technological Variation in the Microprocessor Market". Academy of Management Journal. 39 (5): 1218–1244. doi:10.2307/256997. ISSN 0001-4273. JSTOR 256997.

The sponsors that did not use RISC technology were NEC, AT&T, and Followers of the TRON standard. All three of these microprocessors were specialized for users for whom performance was the highest priority. The Hitachi microprocessor followed the TRON standard, a high-performance CISC technology that, Japanese developers suggested, would be a viable alternative to RISC. The AT&T chip was portrayed as a chip suitable for building top-of-the-line, minicomputer-like computing systems. Similarly, NEC's V60 and V70 were patterned after one of NEC's 36-bit mainframe computers.

-

Komoto, Yasuhiko; Saito, Tatsuya; Mine, Kazumasa (1990-08-25). "Overview of 32-bit V-Series Microprocessor" (pdf). Journal of Information Processing. 13 (2): 110–122. ISSN 1882-6652. Retrieved 2018-01-08.

Open Access

Abstract:

The advances in semiconductor manufacturing technology make it possible to integrate a floating-point unit and a memory management unit noto one microprocessor chip. They also permit the designers of a microprocessor to implement techniques used in the design of mainframe computers especially with regard to pipeline structures. The architecture of the V60 V70 and V80 was made possible by there advances. The V60 and V70 are NEC's first 32-bit microprocessors and include almost all the functions required by applied systems in a chip. The instruction set provides a high-level-language-oriented structure operating system sup-port functions and support functions for highly reliable systems. The V80 also employs the same architecture and achieves higher performance by means of cache memories and branch prediction mechanisms. The V80achieved a performance from two to four times higher than that of the V70. -

Kaneko, Hiraoki; Suzuki, Nariko; Wabuka, Hiroshi; Maemura, Koji (1 March 1990). "Realizing the V80 and its system support functions". IEEE Micro. ACM. 10 (2): 56–69. doi:10.1109/40.52947. ISSN 0272-1732. S2CID 2634866.

Abstract:

An overview is given of the architecture of an overall design considerations for the 11-unit, 32-b V80 microprocessor, which includes two 1-kB cache memories and a branch prediction mechanism that is a new feature for microprocessors. The V80's pipeline processing and system support functions for multiprocessor and high-reliability systems are discussed. Using V80 support functions, multiprocessor and high-reliability systems were realized without any performance drop. Cache memories and a branch prediction mechanism were used to improve pipeline processing. Various hardware facilities replaced the usual microprogram to ensure high performance. -

Shimojima, Takehiko; Teramoto, Masanori (1987). "V60 real-time operating system". Microprocessing and Microprogramming. 21 (1–5): 197–204. doi:10.1016/0165-6074(87)90038-X. ISSN 0165-6074.

Abstract:

This paper describes the requirements for 32-bit microprocessor real-time operating systems, design objectives and the implementation of the V60/V70 Real-Time Operating System (RTOS) and its programming supports. -

Monden, Hiroshi; Teramoto, Takashi; Koga, Masanori (1986-03-14). "V60用アルタイムOSの検討 -32ビットI-TRONに向けて-" [Feasibility study of real-time OS for the V60 - toward for the 32-bit I-TRON -] (PDF). SIG (ARC) Technical Reports (in Japanese). Information Processing Society of Japan. 1986 (19(1985-ARC-061)): 1–8. AN10096105.

Open Access

- "MAME:/src/emu/cpu/v60/v60.c". Mamedev.org. Archived from the original on 2014-02-22. Retrieved 2014-02-15.

- "mamedev/mame". GitHub. Retrieved 17 May 2020.

-

Kimura, S.; Komoto, Y.; Yano, Y. (April 1988). "Implementation of the V60/V70 and its FRM function". IEEE Micro. 8 (2): 22–36. doi:10.1109/40.527. S2CID 9507994.

Abstract:

A description is given of the V60/V70, the first commercially based, general-purpose 32-bit microprocessor in Japan. Its functions include on-chip floating-point operations, a high-level-language-oriented architecture, software debugging support, and support functions to promote a high level of system reliability. Because high reliability is so important, the V60/V70 contains functional redundancy monitoring (FRM) support functions. The discussion covers the overall design considerations, architecture, implementation, hazard detection and control, and FRM functions. The V60/V70 uses a TRON real-time operating system specification. -

Yano, Y.; Koumoto, Y.; Sato, Y. (Spring 1988). "V60/V70 microprocessor and its systems support functions". Digest of Papers. COMPCON Spring 88 Thirty-Third IEEE Computer Society International Conference. pp. 36–42. doi:10.1109/CMPCON.1988.4824. ISBN 0-8186-0828-5. S2CID 9186701.

Abstract:

Two advanced 32-bit microprocessors, the V60 and V70 (mu PD70616 and mu PD70632, respectively), and their support functions for operating systems and high-reliability systems are described. Three operating system functions, namely, the virtual memory support functions, context-switch functions, and asynchronous trap functions are examined. A basic mechanism for high-reliability-system implementation, called FRM (functional redundancy monitoring), is discussed. FRM allows a system to be designed in which multiple V60s (or V70s) form a configuration in which one processor in the system acts as a master while the others act as monitors. An FRM board that uses three V60s in its redundant core is introduced. -

Takahashi, Toshiya; Yano, Yoichi (1988-01-21). "V60/V70アーキテクチャ" [The Architecture of V60/V70 Microprocessors] (PDF). SIG Technical Reports (in Japanese). Information Processing Society of Japan. 1988 (4(1987-ARC-069)): 57–64. AN10096105.

This report describes the architecture of V60/V70 32-bit microprocessors. The architecture integrates various features into a single silicon die, such as a rich set of general-purpose registers, high level language oriented instruction set, floating-point data handling which is suitable for scientific applications, and the FRM (Functionality Redundancy Monitoring) operation mode which supports highly-reliable systems configuration. These features will be introduced. - 1987 Microcomputer Data Book: Vol. 2 (PDF). NEC. August 1986. pp. 3-229–3-232.

-

Yano, Yoichi (April 2012). "32ビット・マイコン「V60」開発物語" [Development story of the 32-bit microcomputer V60] (PDF) (in Japanese). Semiconductor History Museum of Japan. Retrieved 2018-01-08.

"Encore 2012 #75" (pdf). Bulletin "Encore" (in Japanese). Society of Semiconductor Industry Specialists. 75: 17–20. April 2012. Retrieved 2018-01-08. - David T. Methé (1991). Technological Competition in Global Industries: Marketing and Planning Strategies for American Industry. Greenwood Publishing Group. p. 128. ISBN 978-0-89930-480-9.

- Dataquest, "Japanese Semiconductor Industry Service", 1st Quarter 1986, p. 18 (pdf p. 44 in this multi-volume archive)

- Dataquest, "Japanese Semiconductor Industry Service", 1st Quarter 1987, p. 18 (pdf p. 182 in this multi-volume archive)

- "MAME:/src/mame/drivers/model1.c". Mamedev.org. Archived from the original on 2014-04-03. Retrieved 2014-02-15.

- NEC (Oct 1995). "SEMICONDUCTOR SELECTION GUIDE" (PDF) (10th ed.). Archived from the original (PDF) on 2016-03-04.

- "MAME:/src/mame/drivers/ssv.c". Mamedev.org. Archived from the original on 2014-04-03. Retrieved 2014-02-15.

-

Richard Tan. "STS 145 Case Study Sega: The effect of corporate conflict on game design" (PDF). Archived from the original (PDF) on 2014-02-22.

"The Saturn originally ran on a NEC V60 chip at 16MHz. Compare this to the PlayStation CPU (MIPS R3000A 32bit RISC chip) which runs are 33.8MHz, almost double the speed. According to one Sega staff member, when Nakayama first received design specifications for the PlayStation, he was 'the maddest I have ever seen him', calling up the entire R&D division to his office to shout at them. An effort was made to compensate by adding another CPU for dual operation; however, this solution made the system so hard to develop for that, according to Yu Suzuki himself, "only 1 out of 100 programmers could use the Saturn to its full potential."" - "Model Number: PS98-145-HMW, Item Name: PC-UX/V(Rel2.0)(V60)". NEC product sheet.

- Bungou Mini 5RX on YouTube with "high speed outline font smoothing" TV CM

- "Bungo mini 5SX,Bungo mini 7SX,Bungo mini 7SD – Computer Museum". museum.ipsj.or.jp. Retrieved 2017-04-22.

- Takeo, Sakurai; Osamu, Oizumi (1986). "The outline of NEC super minicomputer MS4100 Series, NEC Technical Journal". Nec技報 (in Japanese). NEC Technical Journal, Vol.39 Iss.11 p.p.113-124, Nov. 1986. 39 (11): 113–124.

- "MS-4100 Series - Computer Museum". museum.ipsj.or.jp. Retrieved 2018-01-07.

- "MS4100 Series". dbnst.nii.ac.jp (in Japanese). Retrieved 2018-01-08.

- Dataquest, "Japanese Semiconductor Industry Service", 2nd Quarter 1987, p. 21 (pdf p. 223 in this multi-volume archive)

- "MAME:/src/mame/drivers/segas32.c". Mamedev.org. Archived from the original on 2014-04-03. Retrieved 2014-02-15.

- "MAME:/src/mame/drivers/ms32.c". Mamedev.org. Archived from the original on 2014-04-03. Retrieved 2014-02-15.

- "Kibo HANDBOOK" (PDF). JAXA. September 2007. p. 101.

- "Space Environment Data Acquisition equipment-Attached Payload (SEDA/AP)". iss.jaxa.jp. JAXA. 2007-03-30.

- "JAXA's LSI (MPU/ASIC) roadmap, p. 9; excl. front" (PDF). Development Status for JAXA Critical Parts, 2008. JAXA.

- "Development Status of JAXA EEE Parts" (PDF). Development Status for JAXA Critical Parts, 2008. JAXA.

- MIPS64 5Kf Processor Core Datasheet (PDF) (01.04 ed.). MIPS Technologies Inc. 2005-01-31. Archived from the original (PDF) on 2018-02-20.

- HAYASHI, N. Guidance Control Computer for Launch Vehicle, NEC Technical Journal, Vol. 6, No. 1/2001, pp. 145-148

- "Database of JAXA Qualified EEE Parts and Material: Critical Parts". JAXA. Retrieved 2018-01-07.

- Voica, Alex (2015-07-29). "Back to the future: 64-bit MIPS CPU explores the origins of the solar system – MIPS". mips.com. MIPS. Archived from the original on 2018-02-20.

- "国際宇宙ステーション「きぼう」船外プラットフォーム搭載 宇宙環境計測ミッション装置(SEDA-AP)" [Space Environment Data Acquisition Equipment – Attached Payload (SEDA-AP) on the ISS - "Kibo" Exposed Facility] (PDF) (in Japanese). pp. 52–53. Archived from the original (PDF) on 2018-01-26.

- NEC LAUNCHES V80 ANSWER TO INTEL's 80486 - Computer Business Review, 1989-03-15 Balcklist:www.cbronline.com/news/nec_launches_v80_answer_to_intels_80486

- NEC MAY HAVE THE EDGE WITH ITS 930,000 TRANSISTOR V80 ANSWER TO INTEL'S 80486 - Computer Business Review, 1989-04-06 Balcklist:www.cbronline.com/news/nec_may_have_the_edge_with_its_930000_transistor_v80_answer_to_intels_80486

- OSAMU, TSUJI; SATORU, KOMIYAMA; TOSHIYUKI, DOI; TETSUYA, IWAKI (July 1992). "情報機器 工業用コンピュータμPORT-III" [Information-processing equipment.Industrial computer .MU.PORT-III.]. 明電時報 [Meiden Jiho] (in Japanese) (225): 24–32. ISSN 0386-1570.

- HISAO, SASAKI; AKIRA, SATO; TOSHIO, KARAKAMA (May 1993). "工業用コンピュータμPORT-IIIと適用事例" [Applications of industrial computer .MU.PORT-III.]. 明電時報 [Meiden Jiho] (in Japanese) (230): 41–44. ISSN 0386-1570.

-

Majithi, Kenneth (1987). "The New Generation of Microprocessors". IEEE Micro. 7 (4): 4–5. doi:10.1109/MM.1987.304873. ISSN 0272-1732.

The Japanese have been equally aggressive in their new designs of high-performance microprocessors. NEC's V60 and V70 microprocessors use architectures that include not only the MMU but also an arithmetic floating-point unit on chip. Hitachi and Fujitsu have collaborated to produce a family of microprocessors adapted to the TRON operating system. These processors incorporate instruction pipelines as well as instruction and stack caches. However, unlike NEC, their FPU function is off chip. - "GNU Compiler Internals".

- "Google Groups – Some comments on the NEC V60/V70". Retrieved 2017-04-22.

- 雅則, 寺本; 健治, 赤羽; 良彦, 和田; 由紀子, 水橋; 滋, 川又 (October 1986). "PORTING UNIX System V TO THE V60 SYSTEMS" (pdf). 全国大会講演論文集 (in Japanese). Information Society of Japan. 第33回 (アーキテクチャおよびハードウェア): 163–164. Retrieved 2018-01-07.

- Norihisa Suzuki (January 1992). Shared Memory Multiprocessing. MIT Press. p. 195. ISBN 978-0-262-19322-1.

- "The International Symposium on Shared Memory Multiprocessing (ISSMM)" (PDF). Scientific Information Bulletin. Vol. 16, no. 3. Office of Naval Research Asian Office. July–September 1991. pp. 2–3. Archived (PDF) from the original on March 1, 2021.

- Suzuki, Norihisa, ed. (1992). Shared Memory Multiprocessing. MIT Press. pp. 195ff. ISBN 978-026219322-1.

- "Digital Research launches FlexOS 286 Real-Time Manufacturing Operating System". Computer Business Review. 1987-01-15. Archived from the original on 2013-01-18. Retrieved 2018-09-15.

- Brett Glass (6 May 1991). "Answer Line". InfoWorld: 72. ISSN 0199-6649.

- NEC. "Microprocessors and Peripherals Data Book".

- "MetaWare High C/C++". EDM/2.

- Cygnus Solutions. "gcc/gcc-926/config.sub". Apple Inc. Retrieved 2018-01-07.

-

Cygnus Solutions (1999-02-25). "Patch to replace CYGNUS LOCAL with EGCS LOCAL in config.sub". gcc-patches (Mailing list).

Hi Guys,

I would like to submit the following patch. It renames all occurrences of CYGNUS LOCAL to EGCS LOCAL, which seems slightly more accurate! :-)

Cheers

Nick -

Cygnus Solutions (1999-02-25). "Re: Patch to replace CYGNUS LOCAL with EGCS LOCAL in config.sub". gcc-patches (Mailing list).

Seems like a misguided exercise to me.

If the changes are truly Cygnus-specific, they should not be in Egcs. Otherwise, they should be merged into the config.sub master copy (whose maintainer, by the way, in Ben!). - "Embedding with GNU: Newlib". Embedded. 2001-12-28. Retrieved 2023-10-02.

- "Newlib-cygwin.git / history". Sourceware.org. 2020. Retrieved May 22, 2020.

- "Ada 83 Certified Processor List". Archive.adaic.com. 1998-03-31. Retrieved 2014-02-15.

- "MV-4000". Chipcatalog.com. Archived from the original on 2018-01-07. Retrieved 2014-02-15.

- History-of-48series (refers to the EWS 4800 NEC computers)

- Ratcliffe, Mark, ed. (1995). Ada Yearbook 1995. IOS Press. p. 198. ISBN 9789051992182. Retrieved 22 May 2020.

- "Ada Compiler Validation Procedures – Version 5.0". Ada Resource Association. 18 November 1997. Retrieved 22 May 2020.

- "HP Emulators and Development Solutions for NEC V Series Microprocessors" (PDF). Keysight. p. 13. Retrieved 2018-01-07.

- "HP Computer Museum". Retrieved 2018-01-07.

- "64758G V70 20MHz emulation subsystem 512KB". Keysight. Archived from the original on 2018-01-08. Retrieved 2018-01-08.

- "Agilent Test & Measurement Discontinued Products" (PDF). Keysight. p. 97. Archived from the original (PDF) on 2018-01-08. Retrieved 2018-01-08.

- "NEC V80". groups.google.com. Google Groups.

- NEC (June 1989). Intelligent Peripheral Devices Data Book. The Internet Archive, a 501(c)(3) non-profit. p. 18.

- NEC (May 1990). Single-Chip Microcontroller Data Book. The Internet Archive, a 501(c)(3) non-profit. p. 30.

- NEC (April 1999). "SEMICONDUCTORS SELECTION GUIDE" (PDF) (17th ed.). Archived from the original (PDF) on 2018-01-08.

-

Harigai, Hisao; Kusuda, Masaori; Kojima, Shingo; Moriyama, Masatoshi; Ienaga, Takashi; Yano, Yoichi (1992-10-22). "低消費電力・低電圧動作の32ビットマイクロプロセッサV810" [A low power consumption and low voltage operation 32-bit RISC Microprocessor]. SIG Technical Reports, Information Processing Society of Japan. 1992 (82 (1992-ARC-096)): 41–48.

Abstract:

An advanced 32-bit RISC microprocessor for embedded control; V810 is introduced in this paper. The V810 has high performance and application specified functions. V810 dissipates less power than any other RISC chips. The V810 is the first 32-bit RISC microprocessor that operates at 2.2V.

The V810 chip is fabricated by using 0.8μm CMOS double metal layer process technology to integrate 240,000 transistors on a 7.7×7.7mm2 die. - "NEC Wraps ARM into Gate Arrays". EDN. Retrieved 2017-04-22.

-

Suzuki, K.; Arai, T.; Nadehara, K.; Kuroda, I. (1998). "V830R/AV: embedded multimedia superscalar RISC processor". IEEE Micro. 18 (2): 36–47. doi:10.1109/40.671401. ISSN 0272-1732.

Abstract:

The V830R/AV's real-time decoding of MPEG-2 video and audio data enables practical embedded-processor-based multimedia systems. - NEC (May 2005). "Microcontrollers and Development Tools Selection Guide" (PDF).

- "A newer GCC compiler. « Virtual Boy Development Board « Forum « Planet Virtual Boy". planetvb.com. Archived from the original on 2019-05-30.

- "V850 and RH850 Embedded Software Solutions". ghs.com. Green Hills Software.

- "MAMEdev – V60". GitHub. Retrieved 26 May 2020.

Further reading

- Yano, Y; Iwasaki, J; Sato, Y; Iwata, T; Nakagawa, K; Ueda, M (Feb 1986). A 32b CMOS VLSI microprocessor with on-chip virtual memory management. Solid-State Circuits Conference. Digest of Technical Papers. 1986 IEEE International. Vol. XXIX. IEEE. pp. 36–37. doi:10.1109/ISSCC.1986.1156924. S2CID 57668899.

The execution unit (EXU) is a microprogrammed 32b data path processor which has thirty-two 32b general-purpose registers, sixteen 32b scratch-pad registers, a 64b barrel shifter, a 32b arithmetic logic unit (ALU); and a couple of control registers. Three data-buses that are running - Kaneko, H; Miki, Y; Koya, K; Araki, M (November 1986). "A 32-bit CMOS microprocessor with six-stage pipeline structure". Proceedings of 1986 ACM Fall Joint Computer Conference. IEEE Computer Society Press. pp. 1000–1007.

Abstract: 32-bit microprocessors are the key devices which carry high data processing capability, that was obtained by earlier general-purpose computer systems and mini-computer systems, in much lower cost. Earlier 32-bit microprocessors were limited to adopt excellent architecture and design using appropriate hardware by number of devices could be fabricated on a chip. Complex functions such as Virtual Memory management and ...

- Kurosawa, A.; Yamada, K.; Kishimoto, A.; Mori, K.; Nishiguchi, N. (May 1987). "A Practical CAD System Application for Full Custom VLSI Microcomputer Chips". IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems. 6 (3): 364–373. doi:10.1109/TCAD.1987.1270281. ISSN 1937-4151. S2CID 7394658.

Abstract: This paper presents a practical CAD system application for layout and verification, resulting in producible full-cutom VLSI microcomputer chips. The CAD system supports three design methodologies--symbolic layout mixed with mask level layout, compaction as an optimizer, and fully automated verification. For the area optimization, the symbolic layout and compactor subsystem supports a flexible description of orthogonal layout patterns with arbitrary dimensions in a loose placement manner. The layout patterns include path data, polygonal data, and symbolic cells. For power and delay optimization, the compactor compacts layout data, decreasing both resistance and capacitance for wires and ion-implanted layers. This feature is pioneering the new generation compactor. Emphasis should be put on the fact that it can compact layout data to a format 10-15 percent smaller than that accomplished manually. The verification subsystem can detect all kinds of errors, more than 30 items. A novel feature of the electrical rule check is that it investigates complementary logic errors for CMOS circuits. The synergy of those three design methodologies has brought about several significant advantages. One is manpower reduction by more than half, in the most complicated design process for unique random logic. The other is a 1600-transistors compaction output, smaller by 365 mils/sup 2/ than that manually compacted. The circuit implementation on a chip works at more than a 15 MHz clock rate. Another is the first silicon success. It has been accomplished in a full-custom VLSI microcomputer chip consisting of more than 100 000 transistors.

External links

- Die photo of the V60; at Nikkei BP (in Japanese)

- Die photo of the V60; at Semiconductor History Museum of Japan (in Japanese)

- Die photo of the V60, mounted on PGA package (much clear, in Chinese)

- Die photo of the V60 with PGA packaging, removed ceramic cap (in Chinese)

- Photo of the V60 in PGA packaging w/ ceramic cap shield; glass shield

- Blog: PS98-145-HMW kit: "PC-UX/V" w/ 15 disks & "V60 Sub board" for NEC PC-9801 slot (in Japanese)

- Article: V70 in PGA packaging and the H-IIA rocket (in English)

- Photo of NEC V60 CPU board of the Sega Virtua Racing (in English)

- Site: "System 16" - Sega System 32 Hardware (in English)

- Site: "System 16" - Sega Model 1 Hardware (in English)

- Site: "System 16" - Sega System Multi 32 Hardware (in English)

- Original documents for the V60 (μPD70616) & V70 (μPD70632) is available from here.

- Datasheets for the AFPP (μPD72691) is available from here.

- Renesas V850 Family web site

- Renesas RH850 Family web site