Universal Variable Length Code

Las siglas UVLC corresponden a Universal Variable Length Code, es un método que elimina la redundancia estadística en el algoritmo de compresión CAVLC, y se encuentra generalmente en la última etapa en el algoritmo de compresión de vídeo H.264, o MPEG-4 AVC, que es un códec digital de alta compresión estándar capaz de desarrollar una buena calidad de imagen con bit rates sustancialmente menores que los estándares anteriores (MPEG-2, H.263 o MPEG-4 parte 2). Una arquitectura de codificación UVLC propone cumplir los requisitos de TML8.

Es un método de codificación de fuente que codifica la entropía. Sustituye las palabras de código de una fuente, por una longitud proporcional a la frecuencia de salida de dicha palabra. De esta forma se reduce las palabras que salen con mayor frecuencia a una palabra clave menor, reduciendo así la cantidad de datos a transmitir o almacenar.

Dentro del diseño que conforma este codificador, en la etapa de codificación de la entropía podemos encontrarnos dos métodos:

Proceso

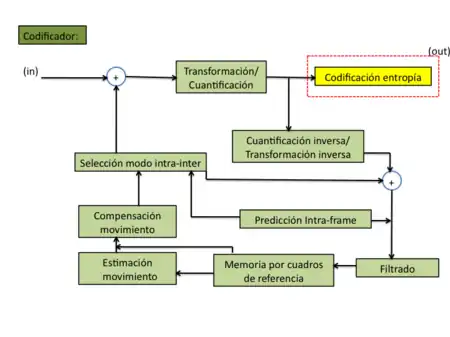

Esquema general

El UVLC se utiliza para codificar la gran mayoría de los elementos de sincronización y cabeceras. Se puede resumir su diseño y funcionamiento en el siguiente diagrama:

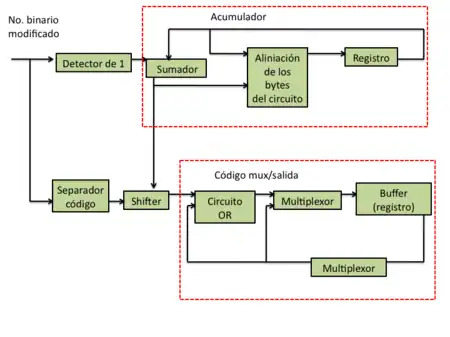

Dos partes:

- Un detector de 1 donde su salida irá a la entrada del acumulador que está formado por un registro, un circuito de alineación de bytes y un sumador.

- Un separador de código que a su salida entrará al código multiplexor/salida que lo forman un circuito OR, un buffer (registro) y dos multiplexores.

Funcionamiento

Este tipo de codificación se basa a la salida en la distribución normal. La relación entre la entrada original de bits y la trama de salida es la siguiente:

| No. palabra clave | Entrada modificada | Código binario | Longitud de los bits | Salida |

|---|---|---|---|---|

| 0 | 1 | 00001 | 1 | 1 |

| 1 | 2 | 00010 | 3 | 001 |

| 2 | 3 | 00011 | 3 | 011 |

| 3 | 4 | 00100 | 5 | 00001 |

| 4 | 5 | 00101 | 5 | 00011 |

| 5 | 6 | 00110 | 5 | 01001 |

| 6 | 7 | 00111 | 5 | 01011 |

| 7 | 8 | 01000 | 7 | 0000001 |

| 8 | 9 | 01001 | 7 | 0000011 |

| 9 | 10 | 01010 | 7 | 0001001 |

| 10 | 11 | 01011 | 7 | 0001011 |

| 11 | 12 | 01100 | 7 | 0100001 |

| 12 | 13 | 01101 | 7 | 0100011 |

| 13 | 14 | 01110 | 7 | 0101001 |

| 14 | 15 | 01111 | 7 | 0101011 |

| 15 | 16 | 10000 | 9 | 000000001 |

La entrada modificada será el número de palabras clave que se quiere codificar más 1, la tercera columna corresponde al código binario de la entrada modificada. La longitud de los bits la determina el detector de 1 a partir de la trama binaria y utilizando la tabla que se muestra posteriormente:

| Entrada (código binario) | Longitud de bits a la salida |

|---|---|

| 0000000000000001 | 1 |

| 000000000000001x | 3 |

| 00000000000001xx | 5 |

| 0000000000001xxx | 7 |

| 000000000001xxxx | 9 |

| 00000000001xxxxx | 11 |

| 0000000001xxxxxx | 13 |

| 000000001xxxxxxx | 15 |

| 00000001xxxxxxxx | 17 |

| 0000001xxxxxxxxx | 19 |

| 000001xxxxxxxxxx | 21 |

| 00001xxxxxxxxxxx | 23 |

| 0001xxxxxxxxxxxx | 25 |

| 001xxxxxxxxxxxxx | 27 |

| 01xxxxxxxxxxxxxx | 29 |

| 1xxxxxxxxxxxxxxx | 31 |

Por ejemplo, si se detecta el bit más significativo en la tercera posición comenzando por el final la trama tendrá una longitud de 5 bits. Así se completa la cuarta columna de la tabla.

El separador de código es un módulo de cableado, que se encarga básicamente de completar la trama de salida añadiendo 0 y 1. Por ejemplo:

- Entrada: 0000 0000 0000 0010

- Salida: 00000000 00000000 00000000 00001001

Se observa que se añaden 0 o 1 para formar bytes completos. Los últimos tres bits formarán el código de salida, mientras que el primer 1 el detector de 1 lo utilizará para detectar la longitud de la trama. El primer bit 1 que se ha añadido para determinar la longitud se eliminará con la aliniación de los bytes, parte incluida en el acumulador, que forman el circuito, además reagrupará los bits e múltiplos de 8.

La salida del separador de código será ajustada por el shifter, que además recibirá los bits del acumulador, para cumplir con las posiciones requerides por el buffer de salida. El circuito OR se usa para combinar la salida del shifter y la salida del bucle que se genera después de la salida del buffer del multiplexor. A la salida del buffer cambiará de acuerdo a una señal de reloj del multiplexor.