Joint Test Action Group

Le JTAG (pour Joint Test Action Group) est le nom de la norme IEEE 1149.1 intitulée « Standard Test Access Port and Boundary-Scan Architecture », qui été normalisée en 1990.

Le terme JTAG, désignant le groupe de travail qui a conçu la norme, est abusivement (mais très largement) utilisé au lieu du terme générique Boundary Scan, ou du sigle TAP (Test Access Port, port d'accès de test).

Principe

La technique de boundary scan (littéralement, « scrutation des frontières ») est conçue pour faciliter et automatiser le test des cartes électroniques numériques. Elle consiste à donner un accès auxiliaire aux broches d'entrée-sortie des composants numériques fortement intégrés.

Initialement, le boundary scan était uniquement destiné au test des courts-circuits et de la continuité entre puces compatibles. Connaissant le schéma électrique de la carte électronique, on applique un ensemble de signaux logiques (appelé « vecteur de test ») sur les broches d'entrée de certains composants (depuis la chaîne boundary scan interne), et on relève les niveaux logiques sur les broches de sortie des composants qui y sont connectés, pour s'assurer qu'ils correspondent aux valeurs attendues. On peut ainsi s'assurer de la bonne qualité des pistes du circuit imprimé et des soudures.

Pour cela, chaque broche d'entrée-sortie n'est pas connectée directement à l'intérieur du composant numérique, mais à travers une « cellule JTAG » permettant de la piloter indépendamment de sa fonction initiale. Il est ainsi possible de la configurer en entrée (haute-impédance) ou en sortie (niveau logique haut ou bas). Cependant chaque type de broche a un nombre de cellules qui lui est associé. Les broches d'entrée et de sortie n'ont besoin que d'une cellule chacune. Les broches tristates ayant besoin de deux entrées pour fonctionner (entrée de signal et activation de l'état haute impédance), il faudra donc deux cellules pour pouvoir les tester. Les broches I/O (pour Input/Output, ou encore Entrée/Sortie) sont quant à elles composées d'une sortie ainsi que d'une entrée qui peut être placée en haute impédance. Étant donné ce qui a été dit précédemment, pour mettre à l'état haute impédance, il y a besoin de deux cellules. Il faudra donc en tout pas moins de trois cellules pour pouvoir tester une broche I/O. Il est à noter que les cellules ne sont pas utilisées pour tester les broches d'alimentation, d'horloge et de reset. Les cellules sont connectées entre elles par un bus série faisant le tour de la puce (d'où la notion de « frontière » ou boundary), équivalent à un grand registre à décalage de taille égale ou supérieure au nombre de broches d'entrée-sortie du composant. On appelle ce registre BSR (pour Boundary Scan Register). Le TAP Controller, qui reçoit les signaux JTAG de l'extérieur, permet d'activer et de piloter les cellules selon une séquence normalisée[1].

Applications

Le JTAG n'est pas limité aux tests de continuité. Il est en effet également possible de tester (au moins partiellement) des fonctions logiques combinatoires, même si elles sont composées de puces non compatibles JTAG, en élaborant des vecteurs de test appropriés et à condition que les entrées et sorties de ces fonctions soient connectées à des composants JTAG. De même, il est possible de tester des mémoires en écrivant puis relisant des valeurs de test. Il est même possible de cette manière de programmer des mémoires non-volatiles (EEPROM et Flash, ces dernières nécessitant un protocole particulier).

De plus, le JTAG n'est pas limité aux connexions externes au composant. La norme JTAG est ainsi utilisée pour remplacer les émulateurs de microprocesseurs (systèmes de débug sur carte remplaçant physiquement le composant), en donnant un accès direct à l'intérieur du processeur (points d'arrêt, lecture et écriture des registres internes, des mémoires internes et externes…) sans perturber ses interactions avec l'extérieur. On nomme cette technique ICE (In-Circuit Emulator) ou ICD (In-Circuit Debugger), et elle est omniprésente sur les microprocesseurs et microcontrôleurs modernes.

Le bus JTAG est également utilisé pour programmer les composants logiques programmables (FPGA et CPLD) ainsi que de nombreux microcontrôleurs (grâce à la capacité du JTAG de programmer la mémoires Flash des microcontrôleurs), voire pour déboguer un microprocesseur ou accéder à un « analyseur logique » intégrés dans un FPGA.

Technologie

Le bus JTAG est un bus série synchrone composé des cinq signaux de contrôle suivants :

- TMS (Test Mode Select) : Signal d'activation de la communication JTAG,

- TCK (Test ClocK) : Horloge,

- TDI (Test Data Input) : Entrée des données,

- TDO (Test Data Output) : Sortie des données,

- TRST (Test ReSeT) : Réinitialisation. Ce signal optionnel est actif au niveau bas.

Il est à noter que certaines applications plus modernes sont dotées de signaux additionnels, tels que :

- RTCK, (Returned Test Clock) Signal optionnel permettant de dialoguer sur une fréquence automatiquement corrigée. Plutôt qu'un réglage manuel en Hz

- NRST, (Neutral Test Reset) Réinitialisation neutre matérielle. Signal commutant tout le matériel sur un statut connu du programmeur afin d'initier une communication plus facilement.

Ce signal reste optionnel, cependant en son absence, il faudrait davantage de tentatives afin de se connecter.

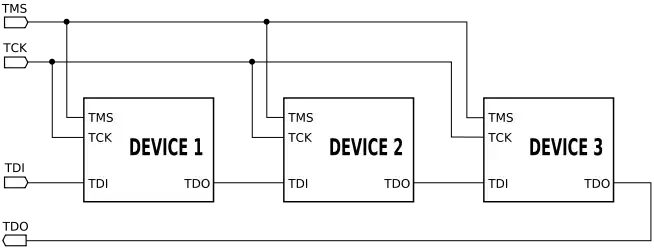

Généralement, les circuits intégrés compatibles « Boundary Scan » montés sur une carte électronique sont associés pour former une chaîne appelée « chaîne JTAG ». On connecte ainsi le signal TDO d'un composant au signal TDI du composant suivant, de manière à former une chaîne. Les autres signaux sont communs à tous les composants de la chaîne.

Il est également possible de chaîner entre elles plusieurs cartes compatibles JTAG, afin de réaliser un test d'un système complet. Cette technique fait l'objet d'une extension de la norme JTAG, nommée IEEE 1149.5.

Un composant boundary scan peut être utilisé selon 4 modes :

- EXTEST : test externe, permettant de commander les broches d'entrée-sortie du composant afin de tester les interconnexions de la carte,

- INTEST : test interne du composant,

- IDCODE : identification du composant,

- BYPASS : mise en haute impédance des entrées-sorties du composant, sa chaîne interne est réduite à un registre afin d'accélérer l'accès à un autre composant de la chaîne.

L'activation d'un mode se fait via la programmation du registre IR (Instruction Register) et l'utilisation d'un mode se fait via l'envoi de données sur le registre DR (Data Register).

Notes et références

- JTAG (Je Teste les ASIC Génialement) par A. Exertier

Voir aussi

Articles connexes

Liens externes

- (en) OpenWrt Wiki Schémas d'interfaces JTAG simples (sur port parallèle de PC)

- Portail de l’électricité et de l’électronique