Microprocesseur

Un microprocesseur est un processeur dont tous les composants ont été suffisamment miniaturisés pour être regroupés dans un unique boîtier. Fonctionnellement, le processeur est la partie d'un ordinateur qui exécute les instructions et traite les données des programmes.

Description

Jusqu'au début des années 1970, les différents composants électroniques, nécessaires au fonctionnement d'un processeur ne pouvaient pas tenir sur un seul circuit intégré, ce qui nécessitait d'interconnecter de nombreux composants dont plusieurs circuits intégrés. En 1971, la société américaine Intel réussit, pour la première fois, à placer tous les composants qui constituent un processeur sur un seul circuit intégré donnant ainsi naissance au microprocesseur[2].

Cette miniaturisation a permis :

- d'augmenter les vitesses[alpha 1] de fonctionnement des processeurs, grâce à la réduction des distances entre les composants ;

- de réduire les coûts, grâce au remplacement de plusieurs circuits par un seul ;

- d'augmenter la fiabilité : en supprimant les connexions entre les composants du processeur, on supprime l'un des principaux vecteurs de panne ;

- de créer des ordinateurs bien plus petits : les micro-ordinateurs ;

- de réduire la consommation énergétique[alpha 2].

Les principales caractéristiques d'un microprocesseur sont :

- Le jeu d'instructions

- qui varie avec le type de microprocesseur et le constructeur : additionner deux nombres, comparer deux nombres pour déterminer s'ils sont égaux, comparer deux nombres pour déterminer lequel est le plus grand, multiplier deux nombres... Un processeur peut exécuter plusieurs dizaines, voire centaines ou milliers, d'instructions différentes.

- La complexité de son architecture

- Cette complexité se mesure par le nombre de transistors contenus dans le microprocesseur. Plus le microprocesseur contient de transistors, plus il pourra effectuer des opérations complexes, et/ou traiter des nombres de grande taille.

- Le nombre de bits que le processeur peut traiter simultanément

- Les premiers microprocesseurs ne pouvaient traiter plus de 4 bits d'un coup. Ils devaient donc exécuter plusieurs instructions pour additionner des nombres de 32 ou 64 bits. En 2007 les microprocesseurs peuvent traiter des nombres sur 64 bits. Le nombre de bits des bus, de la mémoire et du processeur est en rapport direct avec la capacité à traiter de grands nombres rapidement, ou des nombres d'une grande précision (nombres de décimales significatives).

- La vitesse de l’horloge

- Le rôle de l’horloge est de cadencer le rythme du travail du microprocesseur. La fréquence correspond à ce que l'on appelle un cycle d'horloge. Une instruction, selon le type de processeur et d'instruction peut prendre un ou plusieurs cycles d'horloge. Les processeurs RISC sur lequel toutes les opérations en langage machine sont simples mais câblées prend généralement un cycle par instruction. Au contraire, un processeur CISC, contient du microcode, ou une instruction en langage machine, est alors une suite d'instructions câblées. En conséquence, dans tous les cas, à technologie égale, plus la fréquence est élevée, plus le nombre d'instruction pouvant être exécutée est élevée.

Par exemple, un processeur A cadencé à 400 MHz peut exécuter certaines instructions plus rapidement qu'un autre B cadencé à 1 GHz, tout dépend de leurs architectures respectives.

La combinaison des caractéristiques précédentes détermine la puissance du microprocesseur qui s’exprime en « millions d'instructions par seconde » (MIPS). Dans les années 1970, les microprocesseurs effectuaient moins d’un million d’instructions par seconde, mais en 2007, les processeurs pouvaient effectuer plus de 10 milliards d’instructions par seconde.

Histoire

En 1969, le microprocesseur est inventé par un ingénieur et un physicien d'Intel, Marcian Hoff (surnommé Ted Hoff)[4],[5],[6], et Federico Faggin, qui venait de le rejoindre, fort de recherches menées en Italie. Federico Faggin, ingénieur italien est en 1968 chez Fairchild-SGS à Agrate Brianza[7], puis à Palo Alto avec Thomas Klein[7], le concepteur du premier circuit intégré commercial à grilles auto-alignées, le Fairchild 3708, puis chef de projet de la Silicon Gate Technology (SGT), la première méthode pratique pour la fabrication des circuits intégrés MOS (structure semi-conducteur/métal/oxyde) avec grilles auto-alignées, qui a remplacé la grille d'aluminium traditionnelle d'un transistor MOS par une grille en silicium, pour intégrer deux fois plus de transistors dans la même surface. Federico Faggin est embauché par Intel en [7], pour être le chef de projet, le créateur de la méthodologie de conception et le concepteur principal. En seulement quelques mois, avec Marcian Hoff, des quatre puces de l'Intel 4004, qui servit initialement à fabriquer des contrôleurs graphiques en mode texte, il conçut un processeur d'usage général, avec une licence achetée au japonais Busicom[7].

Marcian Hoff a formulé l'architecture du microprocesseur (une architecture de bloc et un jeu d'instructions). Le premier microprocesseur commercialisé, le , est l'Intel 4004 4 bits, suivi par l'Intel 8008 à 8 bits et qui servit initialement à fabriquer des contrôleurs graphiques en mode texte. Jugé trop lent par le client qui en avait demandé la conception, il devint un processeur d'usage général.

Ces processeurs sont les précurseurs des Intel 8080, Zilog Z80, et de la future famille des Intel x86[8]. Federico Faggin est l'auteur d'une méthodologie de conception nouvelle pour la puce et la logique, fondée pour la première fois sur la technologie silicon gate développé par lui en 1968 chez Fairchild. Il a aussi dirigé la conception du premier microprocesseur jusqu'à son introduction sur le marché en 1971[9].

Presque à la même époque la société américaine, Motorola, effectue des travaux et innovations similaires sous la direction de Chuck Peddle[10], venu de General Electric, où il avait conçu une caisse enregistreuse électronique, mais qui décide en 1970 d'abandonner son activité informatique. Il participe au développement du microprocesseur Motorola 6800, à 8 bits, vendu alors 300 US$, et qui va servir aux ordinateurs d'usage professionnel Goupil 1 et 2 de la société SMT.

Dans les années 1970, apparaissent les concepts de datagramme et d'informatique distribuée, avec Arpanet, le réseau Cyclades et la Distributed System Architecture, devenue en 1978 le modèle « OSI-DSA ». Le microprocesseur est très vite accueilli comme la pierre angulaire de cette informatique distribuée, car il permet de décentraliser le calcul, avec des machines moins coûteuses et moins encombrantes face au monopole IBM, produites en plus grande série.

En 1990, Gilbert Hyatt revendique la paternité du microprocesseur en se basant sur un brevet qu’il avait déposé en 1970[11]. La reconnaissance de l’antériorité du brevet de Hyatt aurait permis à ce dernier de réclamer des redevances sur tous les microprocesseurs fabriqués de par le monde, mais le brevet de Hyatt a été invalidé en 1995 par l’office américain des brevets, sur la base du fait que le microprocesseur décrit dans la demande de brevet n'avait pas été réalisé, et n'aurait d'ailleurs pas pu l'être avec la technologie disponible au moment du dépôt du brevet[12].

Le tableau suivant décrit les principales caractéristiques des microprocesseurs fabriqués par Intel, et montre leur évolution en termes de nombre de transistors, en miniaturisation des circuits, et en augmentation de puissance. Il faut garder à l'esprit que si ce tableau décrit l'évolution des produits d'Intel, l'évolution des produits des concurrents a suivi avec plus ou moins d'avance ou de retard la même marche.

Un programme informatique est, par essence, un flux d'instructions exécutées par un processeur. Chaque instruction nécessite un à plusieurs cycles d'horloge, l'instruction est exécutée en autant d'étapes que de cycles nécessaires. Les microprocesseurs séquentiels exécutent l'instruction suivante lorsqu'ils ont terminé l'instruction en cours. Dans le cas du parallélisme d'instructions, le microprocesseur pourra traiter plusieurs instructions dans le même cycle d'horloge, à condition que ces instructions différentes ne mobilisent pas simultanément une unique ressource interne. Autrement dit, le processeur exécute des instructions qui se suivent, et ne sont pas dépendantes l'une de l'autre, à différents stades d'achèvement. Cette file d'exécution à venir s'appelle un pipeline. Ce mécanisme a été implémenté la première fois dans les années 1960 par IBM. Les processeurs plus évolués exécutent en même temps autant d'instructions qu'ils ont de pipelines, ce à la condition que toutes les instructions à exécuter parallèlement ne soient pas interdépendantes, c'est-à-dire que le résultat de l'exécution de chacune d'entre elles ne modifie pas les conditions d'exécution de l'une des autres. Les processeurs de ce type sont appelés processeurs superscalaires. Le premier ordinateur à être équipé de ce type de processeur était le Seymour Cray CDC 6600 en 1965. Le Pentium est le premier des processeurs superscalaires pour compatible PC.

Les concepteurs de processeurs ne cherchent pas simplement à exécuter plusieurs instructions indépendantes en même temps, ils cherchent à optimiser le temps d'exécution de l'ensemble des instructions. Par exemple le processeur peut trier les instructions de manière que tous ses pipelines contiennent des instructions indépendantes. Ce mécanisme s'appelle l'exécution out-of-order. Ce type de processeur s'est imposé pour les machines grand public des années 1980 et aux années 1990[13]. L'exemple canonique de ce type de pipeline est celui d'un processeur RISC, (reduced instruction set computer) en cinq étapes. Le Intel Pentium 4 dispose de 35 étages de pipeline[14]. Un compilateur optimisé pour ce genre de processeur fournit un code qui sera exécuté plus rapidement.

Pour éviter une perte de temps liée à l'attente de nouvelles instructions, et surtout au délai de rechargement du contexte entre chaque changement de threads, les fondeurs[alpha 3] ont ajouté à leurs processeurs des procédés d'optimisation pour que les threads puissent partager les pipelines, les caches et les registres. Ces procédés, regroupés sous l'appellation Simultaneous Multi Threading, ont été mis au point dans les années 1950. Par contre, pour obtenir une augmentation des performances, les compilateurs doivent prendre en compte ces procédés, il faut donc re-compiler les programmes pour ces types de processeurs. Intel a commencé à produire, début des années 2000, des processeurs implémentant la technologie SMT à deux voies. Ces processeurs, les Pentium 4, peuvent exécuter simultanément deux threads qui se partagent les mêmes pipelines, caches et registres. Intel a appelé cette technologie SMT à deux voies : l’Hyperthreading. Le Super-threading (en) est, quant à lui, une technologie SMT dans laquelle plusieurs threads partagent aussi les mêmes ressources, mais ces threads ne s'exécutent que l'un après l'autre et non simultanément[15].

Depuis longtemps déjà, existait l'idée de faire cohabiter plusieurs processeurs au sein d'un même composant, par exemple les System on Chip. Cela consistait, par exemple, à ajouter au processeur, un coprocesseur arithmétique, un DSP, voire un cache mémoire, éventuellement même l'intégralité des composants que l'on trouve sur une carte mère. Des processeurs utilisant deux ou quatre cœurs sont donc apparus, comme le POWER4 d'IBM sorti en 2001. Ils disposent des technologies citées préalablement. Les ordinateurs qui disposent de ce type de processeurs coûtent moins cher que l'achat d'un nombre équivalent de processeurs. Cependant, les performances ne sont pas directement comparables, cela dépend du problème traité. Des API spécialisées ont été développées afin de tirer parti au mieux de ces technologies, comme le Threading Building Blocks d'Intel.

| Date | Nom | Nombre de transistors |

Finesse de gravure (nm) |

Nombre de cœurs | Fréquence de l'horloge | Largeur des données |

MIPS |

|---|---|---|---|---|---|---|---|

| 1971 | Intel 4004 | 2 300 | 10 000 | 1 | 740 kHz | 4 bits/4 bits bus | 0,06 |

| 1974 | Intel 8080 | 6 000 | 6 000 | 1 | 2 MHz | 8 bits/8 bits bus | 0,64 |

| 1979 | Intel 8088 | 29 000 | 3 000 | 1 | 5 MHz | 16 bits/8 bits bus | 0,33 |

| 1982 | Intel 80286 | 134 000 | 1 500 | 1 | 6 à 16 MHz (20 MHz chez AMD) | 16 bits/16 bits bus | 1 |

| 1985 | Intel 80386 | 275 000 | 1 500 | 1 | 16 à 40 MHz | 32 bits/32 bits bus | 5 |

| 1989 | Intel 80486 | 1 200 000 (800nm) | 1 000 à 800 | 1 | 16 à 100 MHz | 32 bits/32 bits bus | 20 |

| 1993 | Pentium (Intel P5) | 3 100 000 | 800 à 250 | 1 | 60 à 233 MHz | 32 bits/64 bits bus | 100 |

| 1997 | Pentium II | 7 500 000 | 350 à 250 | 1 | 233 à 450 MHz | 32 bits/64 bits bus | 300 |

| 1999 | Pentium III | 9 500 000 | 250 à 130 | 1 | 450 à 1 400 MHz | 32 bits/64 bits bus | 510 |

| 2000 | Pentium 4 | 42 000 000 | 180 à 65 | 1 | 1,3 à 3,8 GHz | 32 bits/64 bits bus | 1 700 |

| 2004 | Pentium 4 D (Prescott) | 125 000 000 | 90 à 65 | 1 | 2.66 à 3,6 GHz | 32 bits/64 bits bus | 9 000 |

| 2006 | Core 2 Duo (Conroe) | 291 000 000 | 65 | 2 | 2,4 GHz (E6600) | 64 bits/64 bits bus | 22 000 |

| 2007 | Core 2 Quad (Kentsfield) | 2*291 000 000 | 65 | 4 | 3 GHz (Q6850) | 64 bits/64 bits bus | 2*22 000 (?) |

| 2008 | Core 2 Duo (Wolfdale) | 410 000 000 | 45 | 2 | 3,33 GHz (E8600) | 64 bits/64 bits bus | ~24 200 |

| 2008 | Core 2 Quad (Yorkfield) | 2*410 000 000 | 45 | 4 | 3,2 GHz (QX9770) | 64 bits/64 bits bus | ~2*24 200 |

| 2008 | Intel Core i7 (Bloomfield) | 731 000 000 | 45 | 4 | 3,33 GHz (Core i7 975X) | 64 bits/64 bits bus | ? |

| 2009 | Intel Core i5/i7 (Lynnfield) | 774 000 000 | 45 | 4 | 3,06 GHz (I7 880) | 64 bits/64 bits bus | 76 383 |

| 2010 | Intel Core i7 (Gulftown) | 1 170 000 000 | 32 | 6 | 3,47 GHz (Core i7 990X) | 64 bits/64 bits bus | 147 600 |

| 2011 | Intel Core i3/i5/i7 (Sandy Bridge) | 1 160 000 000 | 32 | 4 | 3,5 GHz (Core i7 2700K) | 64 bits/64 bits bus | |

| 2011 | Intel Core i7/Xeon (Sandy Bridge-E) | 2 270 000 000 | 32 | 4 à 6 | 3,5 GHz (Core i7 3970X) | 64 bits/64 bits bus | 1 ou 2M |

| 2012 | Intel Core i3/i5/i7 (Ivy Bridge) | 1 400 000 000 | 22 | 4 à 6 | 3,5 GHz (Core i7 3770K) | 64 bits/64 bits bus | |

| 2013 | Intel Core i3/i5/i7 (Haswell) | 1 400 000 000 | 22 | 4 à 6 | 3,8 GHz (Core i7 4770K) | 64 bits/64 bits bus | |

| 2014 | Intel Core i3/i5/i7 (Broadwell) | 1 400 000 000 | 14 | 4 à 10 | 3,8 GHz (Core i7 5775R) | 64 bits/64 bits bus | |

| 2015 | Intel Core i3/i5/i7 (Skylake) | 1 750 000 000 | 14 | 4 à 8 | 4 GHz (Core i7 6700K) | 64 bits/64 bits bus | |

| 2016 | Intel Core i3/i5/i7 (Kabylake) | ? | 14 | 4 | 4.2 GHz (Core i7 7700K) | 64 bits/64 bits bus | |

| 2017 | Intel Core i3/i5/i7 (Coffee Lake) | ? | 14 | 6 | 5.0 GHz (Core i7 8086K) | 64 bits/64 bits bus | |

| 2019 | Intel Core i3/i5/i7 (Coffee Lake) | ? | 14 | 8 | 5.0 GHz (Core i7 9900KS) | 64 bits/64 bits bus | |

| 2019 | Intel Core i3/i5/i7/i9 (Ice Lake) | ? | 10 | 4 | 4.1 GHz (Core i7-1068NG7) | 64 bits/64 bits bus | |

| 2019 | Intel Core i3/i5/i7/i9 (Tiger Lake) | ? | 10 | 4 | 5.0 GHz (Core i7-11375H) | 64 bits/64 bits bus | |

| 2020 | Intel Core i3/i5/i7/i9 (Comet Lake) | ? | 14 | 8 | 5.3 GHz (Core i9-10900K) | 64 bits/64 bits bus | |

| 2021 | Intel Core i3/i5/i7/i9 (Rocket Lake) | ? | 14 | 8 | 5.3 GHz (Core i9-11900K) | 64 bits/64 bits bus | |

| 2021 | Intel Core i3/i5/i7/i9 (Alder Lake) | ? | 10 | 16 | 5.3 GHz (Core i9-12900K) | 64 bits/64 bits bus | |

| 2023 | Intel Core i3/i5/i7/i9 (Meteor Lake) | ? | 7 | ||||

| 2024 | ? | ? | 2 | ||||

| 2025 | ? | ? | 1.8 |

- Date : l’année de commercialisation du microprocesseur.

- Nom : le nom du microprocesseur.

- Nombre de transistors : le nombre de transistors contenus dans le microprocesseur.

- Finesse de gravure (nm) : la largeur minimale possible (en nanomètres) du canal des transistors, elle sert indirectement d'unité de base (lambda) dans le dimensionnement des autres structure du circuit. En comparaison, l'épaisseur d'un cheveu humain est de 100 microns = 100 000 nm. Le diamètre d’un atome de silicium est de l’ordre de 100 pm=0,1 nm. En 2014, à des finesses de gravure de l’ordre de 10 nm (pour la mémoire), on se retrouve avec certaines structures (comme la couche d'isolation de la grille des transistors) ayant une épaisseur de moins de 4 nm, ce qui fait quelques dizaines d'atomes de silicium. En augmentant la finesse de gravure, on se rapproche des limites en deçà desquelles le comportement électrique des matériaux relève de moins en moins de la physique classique, mais de plus en plus de la mécanique quantique (les électrons traversant la grille des transistors par effet tunnel).

- Fréquence de l’horloge : la fréquence du signal d'horloge interne qui cadence le microprocesseur. MHz = million(s) de cycles par seconde. GHz = milliard(s) de cycles par seconde.

- Largeur des données : le premier nombre indique le nombre de bits sur lequel une opération est faite. Le second nombre indique le nombre de bits transférés à la fois entre la mémoire et le microprocesseur.

- MIPS : le nombre de millions d’instructions, sur des entiers, effectuées par le microprocesseur en une seconde.

Familles

-0322.jpg.webp)

Les microprocesseurs sont habituellement regroupés en familles, en fonction du jeu d'instructions qu'ils exécutent. Si ce jeu d'instructions comprend souvent une base commune à toute la famille, les microprocesseurs les plus récents d'une famille peuvent présenter de nouvelles instructions. La rétrocompatibilité au sein d'une famille n'est donc pas toujours assurée. Par exemple un programme dit compatible x86 écrit pour un processeur Intel 80386[16], qui permet la protection mémoire, pourrait ne pas fonctionner sur des processeurs antérieurs, mais fonctionne sur tous les processeurs plus récents (par exemple un Core Duo d'Intel ou un Athlon d'AMD).

Il existe des dizaines de familles de microprocesseurs. Parmi celles qui ont été les plus utilisées, on peut citer :

La famille la plus connue par le grand public est la famille x86, apparue à la fin des années 1970, développée principalement par les entreprises Intel (fabricant du Pentium), AMD (fabricant de l'Athlon), VIA et Transmeta. Les deux premières entreprises dominent le marché en fabriquant la majorité des microprocesseurs pour micro-ordinateurs compatibles PC et Macintosh depuis 2006.

Le MOS Technology 6502[17] qui a servi à fabriquer les Apple II, Commodore PET, et dont les descendants ont servi au Commodore 64 et aux consoles Atari 2600. Le MOS Technology 6502 a été conçu par d'anciens ingénieurs de Motorola et était très inspiré du Motorola 6800.

Le microprocesseur Zilog Z80 a été largement utilisé dans les années 1980 dans la conception des premiers micro-ordinateurs personnels 8 bits comme le TRS-80, les Sinclair ZX80, ZX81, ZX Spectrum, le standard MSX, les Amstrad CPC et plus tard dans les systèmes embarqués.

La famille Motorola 68000 (aussi appelée m68k) de Motorola animait les premiers Macintosh, les Mega Drive, les Atari ST et les Commodore Amiga. Leurs dérivés (Dragonball, ColdFire) sont toujours utilisés dans des systèmes embarqués.

Les microprocesseurs PowerPC d'IBM et de Motorola équipaient jusqu'en 2006 les micro-ordinateurs Macintosh (fabriqués par Apple). Ces microprocesseurs sont aussi utilisés dans les serveurs de la série P d'IBM et dans divers systèmes embarqués. Dans le domaine des consoles de jeu, des microprocesseurs dérivés du PowerPC équipent la Wii (Broadway), la GameCube (Gekko), Xbox 360 (dérivé à trois cœurs nommé Xenon). La PlayStation 3 est équipée du microprocesseur Cell, dérivé du POWER4, une architecture proche de PowerPC.

Les processeurs d'architecture MIPS animaient les stations de travail de Silicon Graphics, des consoles de jeux comme la PSone, la Nintendo 64 et des systèmes embarqués, ainsi que des routeurs Cisco. C'est la première famille à proposer une architecture 64 bits avec le MIPS R4000 en 1991. Les processeurs du fondeur chinois Loongson, sont une nouvelle génération basées sur les technologies du MIPS, utilisés dans des supercalculateurs et des ordinateurs faible consommation.

La famille ARM est de nos jours utilisée principalement dans les systèmes embarqués, dont de nombreux PDA et smartphones. Elle a précédemment été utilisée par Acorn pour ses Archimedes et RiscPC.

Rapidité d'exécution des instructions

Fréquence de fonctionnement

Les microprocesseurs sont cadencés par un signal d'horloge (signal oscillant régulier imposant un rythme au transfert entre circuit). Au milieu des années 1980, ce signal avait une fréquence de 4 à 8 MHz. Dans les années 2000, cette fréquence atteint 3 GHz. Plus cette fréquence est élevée, plus le microprocesseur peut exécuter à un rythme élevé les instructions de base des programmes mais plus la qualité des bus doit être soignée et leur longueur adaptée à la fréquence.

L'augmentation de la fréquence présente des inconvénients :

- la dissipation thermique[18] d'un circuit donné est proportionnelle à sa fréquence de fonctionnement et au carré de sa tension d'alimentation[19] : cela implique d'avoir une solution de refroidissement du processeur adaptée ;

- la fréquence est notamment limitée par les temps de commutation des portes logiques : il est nécessaire qu'entre deux « coups d'horloge », les signaux numériques aient eu le temps de parcourir tout le trajet nécessaire à l'exécution de l'instruction attendue ; pour accélérer le traitement, il faut agir sur de nombreux paramètres (taille d'un transistor, interactions électromagnétiques entre les circuits, etc.) qu'il devient de plus en plus difficile d'améliorer (tout en s'assurant de la fiabilité des opérations).

Overclocking

L'overclocking consiste à appliquer au microprocesseur une fréquence du signal d'horloge supérieure aux recommandations du fabricant ce qui permet d'exécuter plus d'instructions à chaque seconde. Cela nécessite souvent plus de puissance d'alimentation au risque de dysfonctionnements voire de destruction en cas de surchauffe.

Optimisation du chemin d'exécution

Les microprocesseurs actuels sont optimisés pour exécuter plus d'une instruction par cycle d'horloge, ce sont des microprocesseurs avec des unités d'exécution parallélisées. De plus ils sont dotés de procédures qui « anticipent » les instructions suivantes avec l'aide de la statistique.

Dans la course à la puissance des microprocesseurs, deux méthodes d'optimisation sont en concurrence :

- la technologie RISC (Reduced Instruction Set Computer, jeu d'instructions simple), rapide avec des instructions simples de taille standardisée, facile à fabriquer et dont on peut monter la fréquence de l'horloge sans trop de difficultés techniques ;

- la technologie CISC (Complex Instruction Set Computer), dont chaque instruction complexe nécessite plus de cycles d'horloge, mais qui a en son cœur beaucoup d'instructions précâblées.

Néanmoins, avec la diminution de la taille des puces électroniques et l'accélération des fréquences d'horloge, la distinction entre RISC et CISC a quasiment complètement disparu. Là où des familles tranchées existaient, on observe aujourd'hui des microprocesseurs où une structure interne RISC apporte de la puissance tout en restant compatible avec une utilisation de type CISC (la famille Intel x86 a ainsi subi une transition entre une organisation initialement très typique d'une structure CISC. Actuellement elle utilise un cœur RISC très rapide, s'appuyant sur un système de réarrangement du code à la volée) mis en œuvre, en partie, grâce à des mémoires caches de plus en plus grandes, comportant jusqu'à trois niveaux.

Structure et fonctionnement

Structure d'un microprocesseur

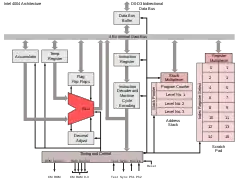

L'unité centrale d'un microprocesseur comprend essentiellement :

- une unité arithmétique et logique (UAL) qui effectue les opérations ;

- des registres qui permettent au microprocesseur de stocker temporairement des données ;

- une unité de contrôle qui commande l'ensemble du microprocesseur en fonction des instructions du programme.

Certains registres ont un rôle très particulier :

- le registre indicateur d'état (flags), ce registre donne l'état du microprocesseur à tout moment, il peut seulement être lu ;

- le compteur de programme (PC, Program Counter), il contient l'adresse de la prochaine instruction à exécuter ;

- le pointeur de pile (SP, Stack Pointer), c'est le pointeur d'une zone spéciale de la mémoire appelée pile où sont rangés les arguments des sous-programmes et les adresses de retour.

Seul le Program Counter est indispensable, il existe de (rares) processeurs ne comportant pas de registre d'état ou pas de pointeur de pile (par exemple le NS320xx (en)).

L'unité de contrôle peut aussi se décomposer :

- le registre d'instruction, mémorise le code de l'instruction à exécuter ;

- le décodeur décode cette instruction ;

- le séquenceur exécute l'instruction, c'est lui qui commande l'ensemble des organes du microprocesseur.

Fonctionnement

Pour commencer, le microprocesseur va charger une instruction contenue en mémoire grâce au compteur de programme. Ce dernier est au passage incrémenté, afin que le processeur traite l'instruction suivante au prochain cycle. L'instruction est alors décodée et si nécessaire le microprocesseur va chercher en mémoire les données supplémentaires. Dans certains cas, des instructions servent uniquement à charger une donnée dans un registre précis ou à écrire une donnée d'un registre en mémoire. Dans ce cas, le processeur charge ou écrit la donnée puis passe à l'instruction suivante. Dans le cas où le processeur doit effectuer une opération de calcul, le processeur fait alors appel à l'ALU. Dans beaucoup d'architectures, celle-ci fonctionne avec un registre accumulateur. Celui-ci enregistre le résultat de l'opération précédente, qui peut ensuite être réutilisé. Dans le cas d'un saut (goto, jump), c'est le compteur de programme qui est directement modifié. Dans le cas d'un saut conditionnel (if), le processeur vérifie avant le saut qu'une condition booléenne est valide (true). Dans certains sauts (jump), le processeur ajoute une valeur à l'accumulateur. Cela permet au programme d'être exécuté à n'importe quel endroit dans la mémoire. Les instructions se divisent donc en plusieurs catégories :

- les instructions de chargement (load) : mettent l'accumulateur à une certaine valeur ;

- les instructions de rangement (store) : permettent d'écrire la valeur de l'accumulateur dans un registre ou un emplacement de mémoire précis ;

- les instructions de saut (if, jump) : permettent de déplacer choisir la prochaine instruction à exécuter ;

- les instructions de calcul (add, mul, div, etc.) : permettent par exemple d'ajouter le contenu du registre X à l'accumulateur, de multiplier l'accumulateur par le registre Y, etc.

À la fin du cycle, le processeur finit de ranger ses données en mémoire ou dans les registres spécifiques. En cas de retenue, un registre spécial reçoit la valeur de la retenue, ce qui permet de le combiner à nouveau pour fonctionner avec plus de bits que ce que permet l'architecture. En cas d'erreur, comme une division par zéro, le processeur modifie un registre d'état et peut déclencher une interruption. Toutes ces étapes peuvent s’effectuer en plusieurs cycles d'horloge. Une optimisation consiste à les exécuter à la chaîne (principe du pipeline) ou en parallèle (architecture superscalaire). Actuellement, face à la difficulté liée à la montée en fréquence des microprocesseurs, les fabricants tentent d'augmenter le nombre d'Instructions Par Cycle (IPC) afin d'augmenter la vitesse de leurs processeurs. Cela a conduit à l'apparition de processeurs multi-cœurs, composés de plusieurs unités, ou cœur, capables d'exécuter une instruction indépendamment de l'autre (contrairement à une architecture superscalaire, qui conserve des registres en commun). On parle alors de calcul en parallèle. Néanmoins, cela nécessite des programmes adaptés et les performances de ces processeurs dépendent donc de plus en plus de la qualité de programmation des programmes qu'ils exécutent.

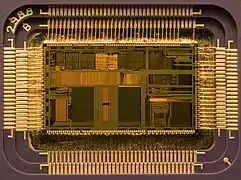

Fabrication

La fabrication d'un microprocesseur est essentiellement identique à celle de n'importe quel circuit intégré. Elle suit donc un procédé complexe. Mais l'énorme taille et complexité de la plupart des microprocesseurs a tendance à augmenter encore le coût de l'opération. La loi de Moore, qui indique que le nombre de transistors des microprocesseurs sur les puces de silicium double tous les deux ans, indique également que les coûts de production doublent en même temps que le degré d'intégration.

La fabrication des microprocesseurs est aujourd'hui considérée comme l'un des deux facteurs d'augmentation de la capacité des unités de fabrication (avec les contraintes liées à la fabrication des mémoires à grande capacité). La finesse de la gravure industrielle a atteint 45 nm en 2006[20]. En diminuant encore la finesse de gravure, les fondeurs se heurtent aux règles de la mécanique quantique.

Problème d'échauffement

Malgré l'usage de techniques de gravures de plus en plus fines, l'échauffement des microprocesseurs reste approximativement proportionnel au carré de leur tension à architecture donnée. Avec la tension, la fréquence, et un coefficient d'ajustement, on peut calculer la puissance dissipée :

Ce problème est lié à un autre, celui de la dissipation thermique et donc souvent des ventilateurs, sources de nuisances sonores. Le refroidissement liquide peut être utilisé. L'utilisation d'une pâte thermique assure une meilleure conduction de la chaleur du processeur vers le radiateur. Si l'échauffement ne pose pas de problème majeur pour des applications type ordinateur de bureau, il en pose pour toutes les applications portables. Il est techniquement facile d'alimenter et de refroidir un ordinateur fixe. Pour les applications portables, ce sont deux problèmes délicats. Le téléphone portable, l'ordinateur portable, l'appareil photo numérique, le PDA, le baladeur MP3 ont une batterie qu'il s'agit de ménager pour que l'appareil portable ait une meilleure autonomie.

Prospective et innovation

- Matériaux bidimensionnels : L'électronique bidimensionnelle[21] est une piste d'innovation envisagée dès 2010[22]. Elle s'appuie sur des microprocesseurs de taille nanométrique[23], imprimé en seulement deux dimensions, à partir de semi-conducteur 2D d'un ou seulement quelques atomes d'épaisseur, afin d'encore miniaturiser l'électronique sous les limites permises par le silicium[24].

Dans les années 2010, des prototypes comprenant quelques transistors ont été testés avec succès.

Des matériaux organiques[25], des nanotubes de carbone[26] ou le disulfure de molybdène sont des matériaux qui semblent prometteurs[27],[28],[29],[30], notamment pour produire des composés souples[31], pouvant par exemple être intégrés dans des feuilles de plastique, des vêtements ou des « robots mous ». Le disulfure de molybdène a été utilisé en 2017 pour fabriquer un semi-conducteur permettant de produire un microprocesseur en quasi 2D, comprenant 115 transistors. Ce dernier a efficacement exécuté des programmes stockés dans une mémoire externe (pour un bit de données mais les auteurs disent que la conception peut être mise à l'échelle pour en gérer plus). À cette échelle les microprocesseurs sont invisibles et pourraient par exemple être intégrés dans le verre de lunettes, de pare-brise ou de vitres ou dans une lentille oculaire.

Notes et références

Notes

- Cette vitesse est exprimé sous forme d'une fréquence exprimée en hertz (Hz), qui comptabilise le nombre de cycles qu'effectue l'horloge de synchronisation du processeur en une seconde.

- Ce n'est pas la seule raison, mais, plus un transistor est petit, moins il a besoin d'énergie pour commuter correctement.

- Société fabricant des puces électroniques.

Références

- (en) « 4004 - 4 bits microprocessor » [PDF], sur intel.com (consulté le )

- Le second XXe siècle : (1939-2000) : les 12 thèmes-clés, Paris, Ellipses, coll. « poche », , 702 p. (ISBN 978-2-340-01442-8, OCLC 1004318546), p. 208

- Nanoinformatique - Inventer l'ordinateur du XXIe siècle J.B. Waldner, Hermes Science, London, 2007, (adaptation et actualisation fig : 2.13, p.58)

- (en)The man who invented the microprocessor, sur bbc.com

- (en)"Ted" Hoff's first microprocessor, sur silicon-valley-story.de, consulté le 25 décembre 2016

- FRANCOIS FRANCIS BUS, L'EPOQUE OU LES PUCES FONT LEURS LOIS : histoire des semiconducteurs vecue de chez Texas Instruments., BOOKS ON DEMAND (ISBN 978-2-322-25685-3)

- "Computers Pioneer" par J.A.N Lee

- (en) The Intel 4004 Microprocessor and the Silicon Gate Technology, sur le site intel4004.com, consulté le 7 décembre 2015

- (en)F. Faggin et M. E. Hoff: Standard Parts and Custom Design Merge in a Four-chip Processor Kit. Electronics,

- (en) Nebojsa Matic , [PDF] "PIC microcontrollers, for beginners", mit.edu

- (en)Gilbert Hyatt Files the First General Patent on the Microprocessor, Later Invalidated, sur historyofinformation.com de décembre 1970, consulté le 25 décembre 2016

- (en) « The Intel 4004 Microprocessor and the Silicon Gate Technology », sur intel4004.com (consulté le )

- (Culler et al, p. 15)

- (en) Patt, Yale (avril 2004). "The Microprocessor Ten Years From Now: What Are The Challenges, How Do We Meet Them? « Copie archivée » (version du 8 novembre 2018 sur l'Internet Archive) Modèle:Wmv], sur utexas.edu, consulté le 7 novembre 2007.

- Superthreading with a multithreaded processor, sur arstechnica.com

- « Intel arrête la production de ses anciens processeurs », sur reghardware.co.uk.

- Le jeu d'instructions du 6502/6510 – sur free.fr

- Dissipation thermique dans les systèmes électroniques, sur techniques-ingenieur.fr

- « dissipation thermique dans les composants » [PDF], sur nae.fr

- (en) « Intel First to Demonstrate Working 45nm Chips », sur intel.com

- Fiori, G. et al. Electronics based on two-dimensional materials. Nat. Nanotechnol. 9, 768–779 (2014).

- Mak, K. F., Lee, C., Hone, J., Shan, J. & Heinz, T. F. Atomically thin MoS2: a new direct-gap semiconductor. Phys. Rev. Lett. 105, 136805 (2010).

- Li, L. et al. Black phosphorus field-effect transistors. Nat. Nanotechnol. 9, 372–377 (2014).

- Stefan Wachter, Dmitry K. Polyushkin, Ole Bethge & Thomas Mueller (2017), A microprocessor based on a two-dimensional semiconductor ; Nature Communications 8, Article n°14948 mis en ligne le 11 Avril 2017 ; Doi:10.1038/ncomms14948 (résumé)

- Myny, K. et al. An 8-bit, 40-instructions-per-second organic microprocessor on plastic foil. IEEE J. Solid-State Circuits 47, 284–291 (2012).

- Shulaker, M. M. et al. Carbon nanotube computer. Nature 501, 526–530 (2013).

- adisavljevic, B., Radenovic, A., Brivio, J., Giacometti, V. & Kis, A. Single-layer MoS2 transistors. Nat. Nanotechnol. 6, 147–150 (2011).

- Roy, T. et al. (2015) Dual-gated MoS2/WSe2 van der Waals tunnel diodes and transistors. ACS Nano 9, 2071–2079

- Pu, J. et al. (2012) Highly flexible MoS2 thin-film transistors with ion gel dielectrics. Nano Lett. 12, 4013–4017

- Wang, H. et al. (2012) Integrated circuits based on bilayer MoS2 transistors. Nano Lett. 12, 4674–4680

- Cheng, R. et al. (2014) Few-layer molybdenum disulfide transistors and circuits for high-speed flexible electronics. Nat. Commun. 5, 5143

Voir aussi

Bibliographie

- (en) Jon Stokes, An Illustrated Introduction to Microprocessors and Computer Architecture par Jon Stokes, No Starch Press, 2006, (ISBN 978-1-59327-104-6)

- (en) Grant McFarland, "Microprocessor Design", McGraw-Hill Professional, 2006, (ISBN 978-0-07-145951-8)

- Jean-Baptiste Waldner, Nano-informatique et intelligence quantique - Inventer l'ordinateur du XXIe siècle, Hermes Science, Londres, 2006, (ISBN 2-7462-1516-0)

- (en) David E. Culler ; Jaswinder Pal Singh and Anoop Gupta (1999)., Parallel Computer Architecture : A Hardware/Software Approach, San Francisco (Calif.), Morgan Kaufmann Publishers, , 1025 p. (ISBN 978-1-55860-343-1 et 1-55860-343-3, lire en ligne).

- (en)Federico Faggin, et al.: The MCS-4 An LSI Microcomputer System. IEEE 1972 Region Six Conference

- (en)Yale Patt, Sanjay J. Patel, Introduction to Computing Systems: From Bits and Gates to C and Beyond, Mc Graw Hill

- (en)Wade Warner, Great moments in microprocessor history, 2004, IBM

Articles connexes

Liens externes

- Portail de l’électricité et de l’électronique

- Portail de l’informatique

- Portail des technologies

.png.webp)