Tensor Processing Unit

Tensor Processing Unit (TPU) is an AI accelerator application-specific integrated circuit (ASIC) developed by Google for neural network machine learning, using Google's own TensorFlow software.[1] Google began using TPUs internally in 2015, and in 2018 made them available for third party use, both as part of its cloud infrastructure and by offering a smaller version of the chip for sale.

Tensor Processing Unit 3.0 | |

| Designer | |

|---|---|

| Introduced | May 2016 |

| Type | Neural network Machine learning |

Overview

The tensor processing unit was announced in May 2016 at Google I/O, when the company said that the TPU had already been used inside their data centers for over a year.[2][3] The chip has been specifically designed for Google's TensorFlow framework, a symbolic math library which is used for machine learning applications such as neural networks.[4] However, as of 2017 Google still used CPUs and GPUs for other types of machine learning.[2] Other AI accelerator designs are appearing from other vendors also and are aimed at embedded and robotics markets.

Google's TPUs are proprietary. Some models are commercially available, and on February 12, 2018, The New York Times reported that Google "would allow other companies to buy access to those chips through its cloud-computing service."[5] Google has said that they were used in the AlphaGo versus Lee Sedol series of man-machine Go games,[3] as well as in the AlphaZero system, which produced Chess, Shogi and Go playing programs from the game rules alone and went on to beat the leading programs in those games.[6] Google has also used TPUs for Google Street View text processing and was able to find all the text in the Street View database in less than five days. In Google Photos, an individual TPU can process over 100 million photos a day.[2] It is also used in RankBrain which Google uses to provide search results.[7]

Compared to a graphics processing unit, it is designed for a high volume of low precision computation (e.g. as little as 8-bit precision)[8] with more input/output operations per joule, without hardware for rasterisation/texture mapping.[3] The TPU ASICs are mounted in a heatsink assembly, which can fit in a hard drive slot within a data center rack, according to Norman Jouppi.[2] Different types of processors are suited for different types of machine learning models, TPUs are well suited for CNNs while GPUs have benefits for some fully-connected neural networks, and CPUs can have advantages for RNNs.[9]

Google provides third parties access to TPUs through its Cloud TPU service as part of the Google Cloud Platform[10] and through its notebook-based services Kaggle and Colaboratory.[11][12]

Products[13]

| TPUv1 | TPUv2 | TPUv3 | TPUv4[14][15] | Edge v1 | |

|---|---|---|---|---|---|

| Date introduced | 2016 | 2017 | 2018 | 2021 | 2018 |

| Process node | 28 nm | 16 nm | 16 nm | 7 nm | |

| Die size (mm2) | 331 | < 625 | < 700 | < 400 | |

| On-chip memory (MiB) | 28 | 32 | 32 | 144 | |

| Clock speed (MHz) | 700 | 700 | 940 | 1050 | |

| Memory | 8GB DDR3 | 16GB HBM | 32GB HBM | 32GB HBM | |

| TDP (W) | 75 | 280 | 450 | 170 | 2 |

| TOPS (Tera Operations Per Second) | 23 | 45 | 90 | 275 | 4 |

| TOPS/W | 0.3 | 0.16 | 0.2 | 1.6 | 2 |

First generation TPU

The first-generation TPU is an 8-bit matrix multiplication engine, driven with CISC instructions by the host processor across a PCIe 3.0 bus. It is manufactured on a 28 nm process with a die size ≤ 331 mm2. The clock speed is 700 MHz and it has a thermal design power of 28–40 W. It has 28 MiB of on chip memory, and 4 MiB of 32-bit accumulators taking the results of a 256×256 systolic array of 8-bit multipliers.[16] Within the TPU package is 8 GiB of dual-channel 2133 MHz DDR3 SDRAM offering 34 GB/s of bandwidth.[17] Instructions transfer data to or from the host, perform matrix multiplications or convolutions, and apply activation functions.[16]

Second generation TPU

The second-generation TPU was announced in May 2017.[18] Google stated the first-generation TPU design was limited by memory bandwidth and using 16 GB of High Bandwidth Memory in the second-generation design increased bandwidth to 600 GB/s and performance to 45 teraFLOPS.[17] The TPUs are then arranged into four-chip modules with a performance of 180 teraFLOPS.[18] Then 64 of these modules are assembled into 256-chip pods with 11.5 petaFLOPS of performance.[18] Notably, while the first-generation TPUs were limited to integers, the second-generation TPUs can also calculate in floating point. This makes the second-generation TPUs useful for both training and inference of machine learning models. Google has stated these second-generation TPUs will be available on the Google Compute Engine for use in TensorFlow applications.[19]

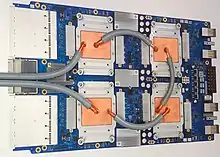

Third generation TPU

The third-generation TPU was announced on May 8, 2018.[20] Google announced that processors themselves are twice as powerful as the second-generation TPUs, and would be deployed in pods with four times as many chips as the preceding generation.[21][22] This results in an 8-fold increase in performance per pod (with up to 1,024 chips per pod) compared to the second-generation TPU deployment.

Fourth generation TPU

On May 18, 2021, Google CEO Sundar Pichai spoke about TPU v4 Tensor Processing Units during his keynote at the Google I/O virtual conference. TPU v4 improved performance by more than 2x over TPU v3 chips. Pichai said "A single v4 pod contains 4,096 v4 chips, and each pod has 10x the interconnect bandwidth per chip at scale, compared to any other networking technology.”[23]

Edge TPU

In July 2018, Google announced the Edge TPU. The Edge TPU is Google's purpose-built ASIC chip designed to run machine learning (ML) models for edge computing, meaning it is much smaller and consumes far less power compared to the TPUs hosted in Google datacenters (also known as Cloud TPUs[24]). In January 2019, Google made the Edge TPU available to developers with a line of products under the Coral brand. The Edge TPU is capable of 4 trillion operations per second with 2 W of electrical power.[25]

The product offerings include a single-board computer (SBC), a system on module (SoM), a USB accessory, a mini PCI-e card, and an M.2 card. The SBC Coral Dev Board and Coral SoM both run Mendel Linux OS – a derivative of Debian.[26][27] The USB, PCI-e, and M.2 products function as add-ons to existing computer systems, and support Debian-based Linux systems on x86-64 and ARM64 hosts (including Raspberry Pi).

The machine learning runtime used to execute models on the Edge TPU is based on TensorFlow Lite.[28] The Edge TPU is only capable of accelerating forward-pass operations, which means it's primarily useful for performing inferences (although it is possible to perform lightweight transfer learning on the Edge TPU[29]). The Edge TPU also only supports 8-bit math, meaning that for a network to be compatible with the Edge TPU, it needs to either be trained using the TensorFlow quantization-aware training technique, or since late 2019 it's also possible to use post-training quantization.

On November 12, 2019, Asus announced a pair of single-board computer (SBCs) featuring the Edge TPU. The Asus Tinker Edge T and Tinker Edge R Board designed for IoT and edge AI. The SBCs officially support Android and Debian operating systems.[30][31] ASUS has also demonstrated a mini PC called Asus PN60T featuring the Edge TPU.[32]

On January 2, 2020, Google announced the Coral Accelerator Module and Coral Dev Board Mini, to be demonstrated at CES 2020 later the same month. The Coral Accelerator Module is a multi-chip module featuring the Edge TPU, PCIe and USB interfaces for easier integration. The Coral Dev Board Mini is a smaller SBC featuring the Coral Accelerator Module and MediaTek 8167s SoC.[33][34]

Pixel Neural Core

On October 15, 2019, Google announced the Pixel 4 smartphone, which contains an Edge TPU called the Pixel Neural Core.[35]

See also

- Cognitive computer

- Neural processing unit

- Structure tensor, a mathematical foundation for TPU's

- Tensor Core, a similar architecture proposed by Nvidia

- TrueNorth, a similar device simulating spiking neurons instead of low-precision tensors

- Vision processing unit, a similar device specialised for vision processing

References

- "Cloud Tensor Processing Units (TPUs)". Google Cloud. Retrieved 20 July 2020.

- "Google's Tensor Processing Unit explained: this is what the future of computing looks like". TechRadar. Retrieved 2017-01-19.

- Jouppi, Norm (May 18, 2016). "Google supercharges machine learning tasks with TPU custom chip". Google Cloud Platform Blog. Retrieved 2017-01-22.

- "TensorFlow: Open source machine learning" "It is machine learning software being used for various kinds of perceptual and language understanding tasks" — Jeffrey Dean, minute 0:47 / 2:17 from Youtube clip

- "Google Makes Its Special A.I. Chips Available to Others". The New York Times. Retrieved 2018-02-12.

- McGourty, Colin (6 December 2017). "DeepMind's AlphaZero crushes chess". chess24.com.

- "Google's Tensor Processing Unit could advance Moore's Law 7 years into the future". PCWorld. Retrieved 2017-01-19.

- Armasu, Lucian (2016-05-19). "Google's Big Chip Unveil For Machine Learning: Tensor Processing Unit With 10x Better Efficiency (Updated)". Tom's Hardware. Retrieved 2016-06-26.

- Wang, Yu Emma; Wei, Gu-Yeon; Brooks, David (2019-07-01). "Benchmarking TPU, GPU, and CPU Platforms for Deep Learning". arXiv:1907.10701 [cs.LG].

- "Frequently Asked Questions | Cloud TPU". Google Cloud. Retrieved 2021-01-14.

- "Google Colaboratory". colab.research.google.com. Retrieved 2021-05-15.

- "Use TPUs | TensorFlow Core". TensorFlow. Retrieved 2021-05-15.

- https://conferences.computer.org/iscapub/pdfs/ISCA2021-4ghucdBnCWYB7ES2Pe4YdT/333300a001/333300a001.pdf

- Stay tuned, more information on TPU v4 is coming soon, retrieved 2020-08-06.

- Cloud TPU System Architecture, retrieved 2022-10-15.

- Jouppi, Norman P.; Young, Cliff; Patil, Nishant; Patterson, David; Agrawal, Gaurav; Bajwa, Raminder; Bates, Sarah; Bhatia, Suresh; Boden, Nan; Borchers, Al; Boyle, Rick; Cantin, Pierre-luc; Chao, Clifford; Clark, Chris; Coriell, Jeremy; Daley, Mike; Dau, Matt; Dean, Jeffrey; Gelb, Ben; Ghaemmaghami, Tara Vazir; Gottipati, Rajendra; Gulland, William; Hagmann, Robert; Ho, C. Richard; Hogberg, Doug; Hu, John; Hundt, Robert; Hurt, Dan; Ibarz, Julian; Jaffey, Aaron; Jaworski, Alek; Kaplan, Alexander; Khaitan, Harshit; Koch, Andy; Kumar, Naveen; Lacy, Steve; Laudon, James; Law, James; Le, Diemthu; Leary, Chris; Liu, Zhuyuan; Lucke, Kyle; Lundin, Alan; MacKean, Gordon; Maggiore, Adriana; Mahony, Maire; Miller, Kieran; Nagarajan, Rahul; Narayanaswami, Ravi; Ni, Ray; Nix, Kathy; Norrie, Thomas; Omernick, Mark; Penukonda, Narayana; Phelps, Andy; Ross, Jonathan; Ross, Matt; Salek, Amir; Samadiani, Emad; Severn, Chris; Sizikov, Gregory; Snelham, Matthew; Souter, Jed; Steinberg, Dan; Swing, Andy; Tan, Mercedes; Thorson, Gregory; Tian, Bo; Toma, Horia; Tuttle, Erick; Vasudevan, Vijay; Walter, Richard; Wang, Walter; Wilcox, Eric; Yoon, Doe Hyun (June 26, 2017). In-Datacenter Performance Analysis of a Tensor Processing Unit™. Toronto, Canada. arXiv:1704.04760.

- Kennedy, Patrick (22 August 2017). "Case Study on the Google TPU and GDDR5 from Hot Chips 29". Serve The Home. Retrieved 23 August 2017.

- Bright, Peter (17 May 2017). "Google brings 45 teraflops tensor flow processors to its compute cloud". Ars Technica. Retrieved 30 May 2017.

- Kennedy, Patrick (17 May 2017). "Google Cloud TPU Details Revealed". Serve The Home. Retrieved 30 May 2017.

- Frumusanu, Andre (8 May 2018). "Google I/O Opening Keynote Live-Blog". Retrieved 9 May 2018.

- Feldman, Michael (11 May 2018). "Google Offers Glimpse of Third-Generation TPU Processor". Top 500. Retrieved 14 May 2018.

- Teich, Paul (10 May 2018). "Tearing Apart Google's TPU 3.0 AI Coprocessor". The Next Platform. Retrieved 14 May 2018.

- "Google Launches TPU v4 AI Chips". www.hpcwire.com. 20 May 2021. Retrieved June 7, 2021.

- "Cloud TPU". Google Cloud. Retrieved 2021-05-21.

- "Edge TPU performance benchmarks". Coral. Retrieved 2020-01-04.

- "Dev Board". Coral. Retrieved 2021-05-21.

- "System-on-Module (SoM)". Coral. Retrieved 2021-05-21.

- "Bringing intelligence to the edge with Cloud IoT". Google Blog. 2018-07-25. Retrieved 2018-07-25.

- "Retrain an image classification model on-device". Coral. Retrieved 2019-05-03.

- "組込み総合技術展&IoT総合技術展「ET & IoT Technology 2019」に出展することを発表". Asus.com (in Japanese). Retrieved 2019-11-13.

- Shilov, Anton. "ASUS & Google Team Up for 'Tinker Board' AI-Focused Credit-Card Sized Computers". Anandtech.com. Retrieved 2019-11-13.

- Aufranc, Jean-Luc (2019-05-29). "ASUS Tinker Edge T & CR1S-CM-A SBC to Feature Google Coral Edge TPU & NXP i.MX 8M Processor". CNX Software - Embedded Systems News. Retrieved 2019-11-14.

- "New Coral products for 2020". Google Developers Blog. Retrieved 2020-01-04.

- "Accelerator Module". Coral. Retrieved 2020-01-04.

- "Introducing the Next Generation of On-Device Vision Models: MobileNetV3 and MobileNetEdgeTPU". Google AI Blog. Retrieved 2020-04-16.